# Full Adder Design

Design Practice - MyCAD

# **Table of Contents**

- Preface

- XOR2 Design

- XOR2 schematic and symbol

- XOR2 simulation

- XOR2 layout and results of verification

- AND2 Gate Design

- AND2 gate schematic and symbol

- AND2 simulation

- AND2 gate layout and results of verification

- OR2 Gate Design

- AND2 gate schematic and symbol

- AND2 simulation

- AND2 gate layout and results of verification

- Half Adder Design

- Half Adder schematic and symbol

- Half Adder simulation

- Half Adder layout and results of verification

- Full Adder Design

- Full Adder schematic and symbol

- Full Adder simulation

- Full Adder layout and results of verification

## **Preface**

- This document provides the information on how to design Full Adder schematic and layout.

- Full Adder is designed based on MOSIS SCMOS layout rules.

- If you want to get more information, please refer to the related documents as below.

- MyCAD Tutorial :

Learn how to use schematic and layout editor.

- MySpice Tutorial :Learn about simulating a circuit.

- MyChip Pro Verification Reference Manual :

Look up specific verification commands.

Copyright © 1992 – 2006, SELOCO Incorporated.

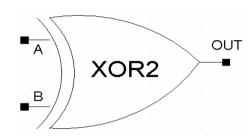

# **XOR2** schematic and symbol

Logic Symbol

| А | В | OUT |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 1   |

| 1 | 0 | 1   |

| 1 | 1 | 0   |

**Truth Table**

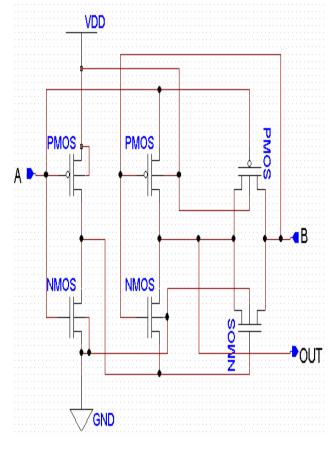

Schematic

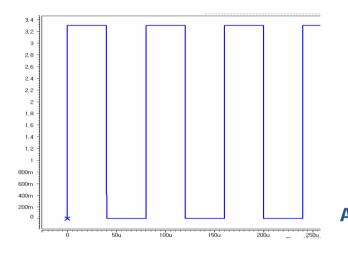

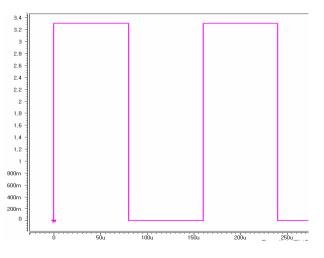

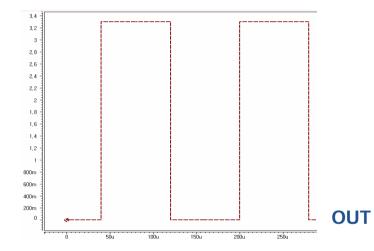

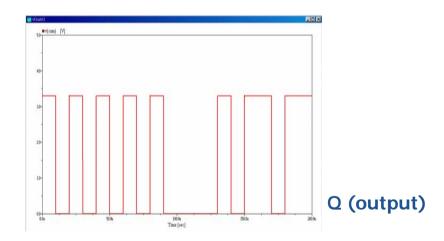

## **XOR2 Simulation**

B

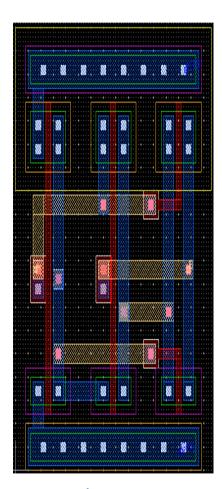

## XOR2 layout and results of verification

Layout

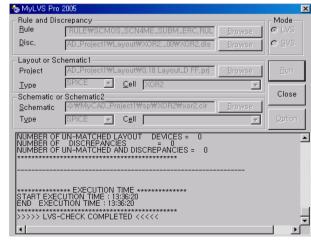

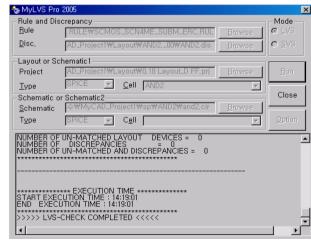

LVS result

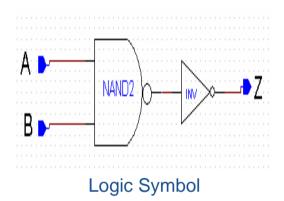

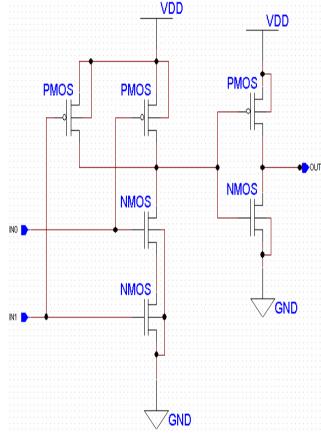

## AND2 gate schematic and symbol

Input

Output

A

B

OUT

0

0

0

0

1

0

1

0

0

1

1

1

**Truth Table**

**Schematic**

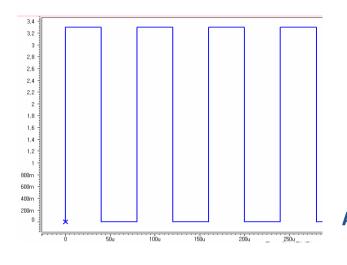

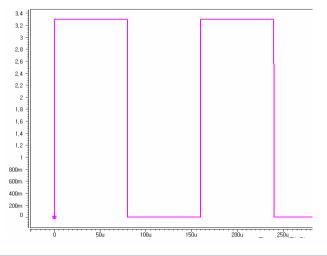

#### **AND2 Simulation**

B

Z

## AND2 layout and results of verification

Layout

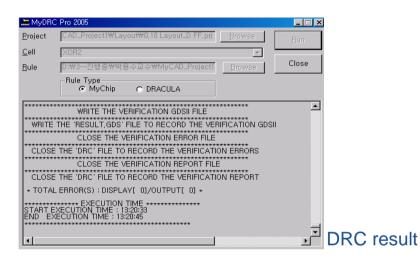

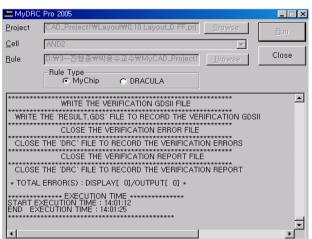

DRC result

LVS result

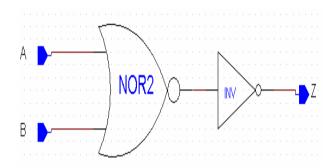

## **OR2** gate schematic and symbol

Logic Symbol

| Input |   | Output |  |

|-------|---|--------|--|

| А     | В | Z      |  |

| 0     | 0 | 0      |  |

| 0     | 1 | 1      |  |

| 1     | 0 | 1      |  |

| 1     | 1 | 1      |  |

**Truth Table**

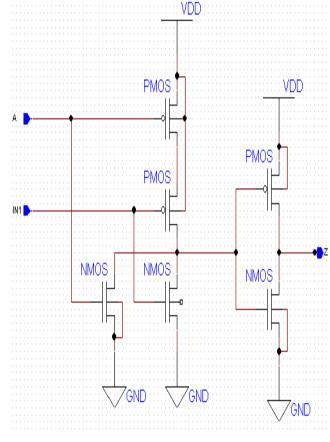

**Schematic**

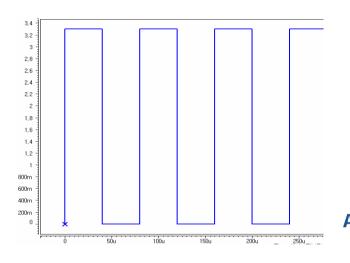

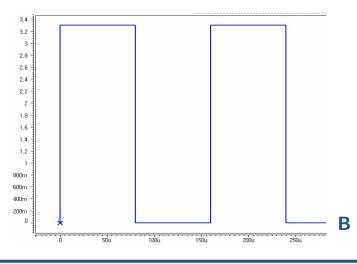

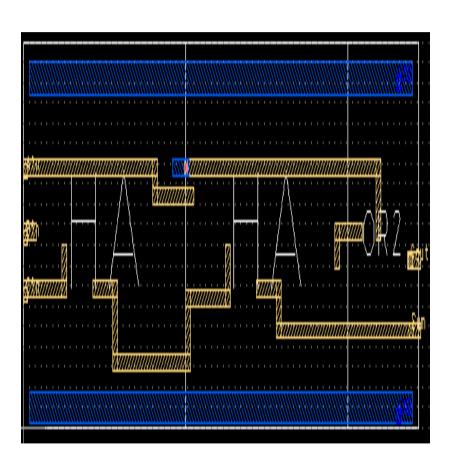

## **OR2 Simulation**

Z

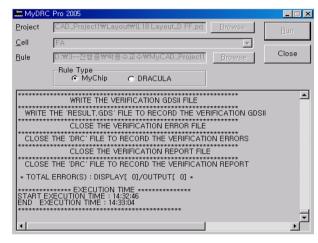

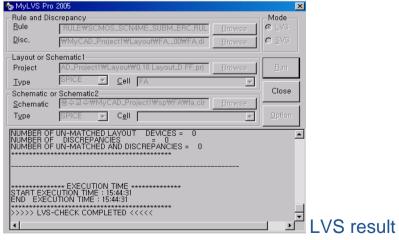

# OR2 layout and results of verification MyCALT

Layout

DRC result

LVS result

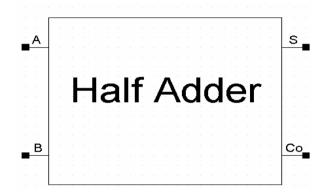

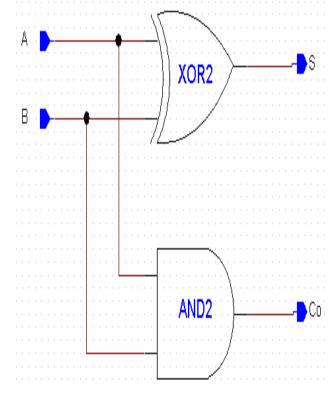

# HA schematic and symbol

Logic Symbol

| А | В | S | C0 |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 1 | 1 | 0  |

| 1 | 0 | 1 | 0  |

| 1 | 1 | 0 | 1  |

**Truth Table**

Schematic

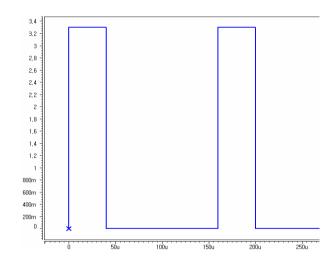

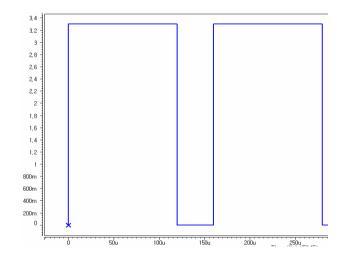

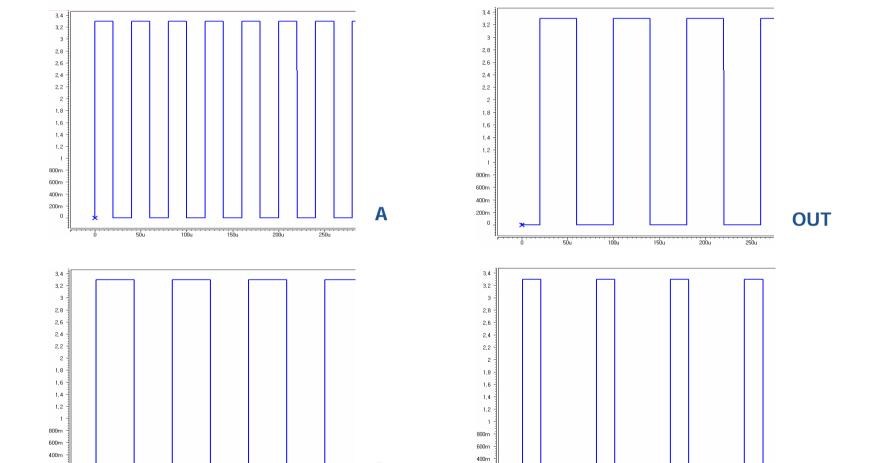

## HA Simulation

50u

100u

150u

200m

B

Co

150u

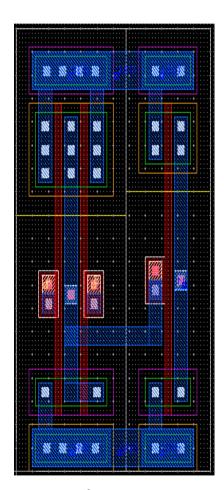

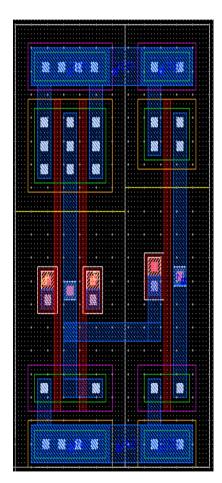

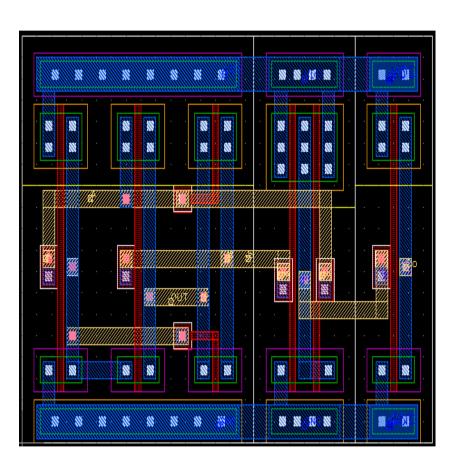

## HA layout and results of verification

DRC result

Layout

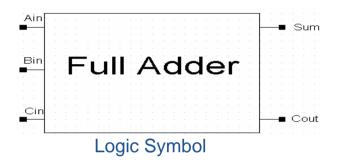

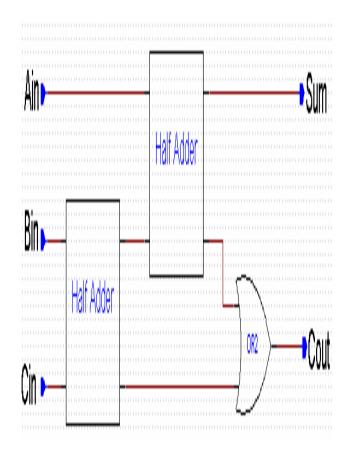

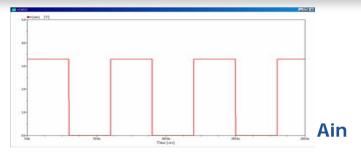

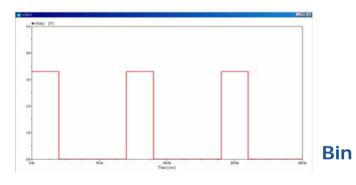

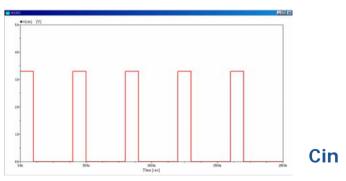

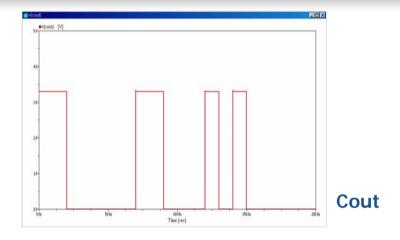

# FA schematic and symbol

| Input |     | Output |     |      |

|-------|-----|--------|-----|------|

| Ain   | Bin | Cin    | Sum | Cout |

| 0     | 0   | 0      | 0   | 0    |

| 0     | 0   | 1      | 1   | 0    |

| 0     | 1   | 0      | 1   | 0    |

| 0     | 1   | 1      | 0   | 1    |

| 1     | 0   | 0      | 1   | 0    |

| 1     | 0   | 1      | 0   | 1    |

| 1     | 1   | 0      | 0   | 1    |

| 1     | 1   | 1      | 1   | 1    |

**Truth Table**

**Schematic**

# **FA Flip-Flop Simulation**

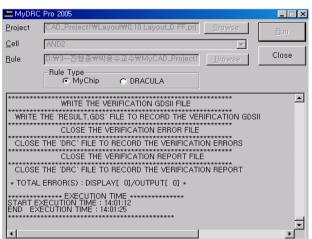

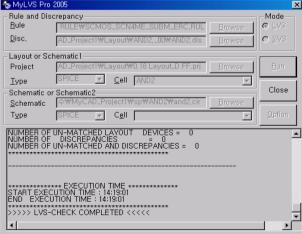

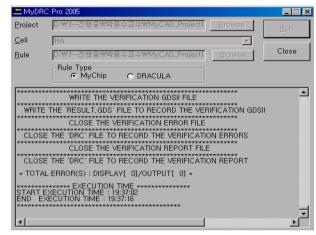

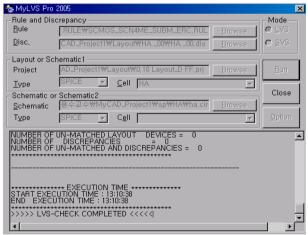

# FA layout and results of verification

DRC result

Layout

The End