# MyCAD Analog Design Practice Amplifier

MyAnalog Station & MyChip Station Pro

**Copyright Information**

MyChip Station Pro 2005 is produced by SELOCO Incorporated.

Unauthorized copying, duplication, or other reproduction is prohibited without the written consent of

SELOCO,Inc..

This document is protected by copyright and distributed under licenses restricting its use, copyrigh, and

distribution. No part of this document may be reproduced in any form by any means without prior written

authorization of SELOCO, Inc and its licensors, if any.

Copyright © 1992 – 2006, SELOCO Incorporated.

Copyright © 1992 - 2006 LayEdProRef.doc, MyCAD Incorporated.

All rights reserved. Confidential. Online documentation may be printed by licensed customers of SELOCO

Incorporated for internal business purposes only.

Published: May 2006

SELOCO, Inc.

3F Namyang Bldg, 60-5 Bangi-dong

Songpa-gu, Seoul, 138-828 Korea

Phone: +82-2-3433-0000

Fax: +82-2-3433-0099

E-mail: support@seloco.com, sales@seloco.com

Home page: http://www.seloco.com

MyCAD, Inc.

528 E. Weddell Drive, Suite #3

Sunnyvale, California 94089, USA

Phone: 408-745-6785 Fax: 408-745-6783

Email: support@mycad.com, sales@mycad.com

Home page: <a href="http://www.mycad.com">http://www.mycad.com</a>

2

# 목 차

| 1. | MyCAD    | 소개                                        | 5  |

|----|----------|-------------------------------------------|----|

|    | 1.1.     | MyChip Station Pro                        | 6  |

|    | (1)      | LayEd Pro                                 | 7  |

|    | (2)      | MyDRC Pro                                 | 7  |

|    | (3)      | LayNet Pro                                | 8  |

|    | (4)      | MyLVS Pro                                 | 8  |

|    | (5)      | CifGDS Pro                                | 8  |

|    | 1.2.     | MyAnalog Station                          | 9  |

|    | (1)      | Schematic Editor                          | 9  |

|    | (2)      | Logic2SPICE                               | 9  |

|    | (3)      | MySPICE                                   | 10 |

|    | (4)      | MyGPP                                     | 10 |

| 2. | Tutorial | 실습 목적 및 예제                                | 11 |

|    | 2.1.     | Tutorial 실습 목적                            | 11 |

|    | 2.2.     | MyCAD Tutorial 실습 환경                      | 11 |

|    | (1)      | 설계 환경 파일 & 환경 설정                          | 11 |

|    |          | ① MyAnalog Station                        | 11 |

|    |          | ② MyChip Station Pro                      | 11 |

|    |          | ③ 실습환경                                    | 12 |

|    |          | ④ 중요 File 설명                              | 13 |

|    | (2)      | 설계 후 생성되는 파일                              | 14 |

|    | 2.3.     | Two stage amp 이론                          | 15 |

|    | (1)      | Schematic                                 | 15 |

|    | (2)      | Current mirror                            | 15 |

|    |          | ① 개요                                      | 15 |

|    |          | ② 예제 (current mirror simulation)          | 16 |

|    | (3)      | Differential amplifier                    | 18 |

|    |          | ① 개요                                      | 18 |

|    |          | ② 예제 (differential amp simulation)        | 20 |

|    | (4)      | Common source amplifier                   | 23 |

|    |          | ① 개요                                      | 23 |

|    |          | ② 阅제 (common source amplifier simulation) | 24 |

|    | 2.4.     | Two stage amp 설계                          | 27 |

|    | (1)      | Two stage amp 설계                          | 27 |

|    |          | ① Library 생성                              | 27 |

|    |          | ② Schematic 설계                            | 31 |

|    |          | ③ Schematic 검증                            | 34 |

|    |          |                                           |    |

|       | (     | ④ Netlist 파일 추출                                                                | 36  |

|-------|-------|--------------------------------------------------------------------------------|-----|

|       | (     | Simulation                                                                     | 40  |

|       | (2)   | Amp Layout 설계                                                                  | 49  |

|       | (     | ① Project 생성                                                                   | 49  |

|       | (     | ② Layout 설계                                                                    | 53  |

|       | (     | ③ Layout 검증                                                                    | 58  |

|       | (     | ④ SPICE 시뮬레이션 [MySPICE (Analog Circuit Simulation)]                            | 65  |

|       | (3)   | Layout과 Schematic 비교분석                                                         | 71  |

|       | (     | ① Netlist 비교 [MyLVS (Hierarchical Layout Versus Schematic Netlist Comparator)] | 71  |

|       | (     | ② Discrepancy 파일 확인                                                            | 74  |

|       | (     | ③ Layout Spice Simulation과 Schematic Spice Simulation비교                        | 75  |

|       | (4)   | Layout data 변환                                                                 | 76  |

|       | (     | ① CifGDS Pro                                                                   | 76  |

| APPEN | NDIX  |                                                                                | 78  |

| Α     | Tech  | nology File                                                                    | 78  |

|       | A.1.  | SCMOS_SCN4ME_SUBM.TEC                                                          | 78  |

|       | A.2.  | STIPPLE.LST                                                                    | 89  |

| В     | Verit | ication File                                                                   | 90  |

|       | B.1.  | SCMOS_SCN4ME_SUBM_DRC.rul                                                      | 90  |

|       | B.2.  | SCMOS_SCN4ME_SUBM_ERC.rul                                                      | 96  |

|       | B.3.  | SCMOS_SCN4ME_SUBM_ERC(nwell).rul                                               | 100 |

| С     | Spic  | e File                                                                         | 104 |

|       | C.1.  | include.inc (기본 parameter)                                                     | 104 |

|       | C.2.  | Lavout Two stage amp(첨가부분)                                                     | 106 |

# 1. MyCAD 소개

MyCAD는 전자회로설계 및 시뮬레이션용 CAD 프로그램으로서 1990년대 자체 개발을 토대로 하여 국내외로 보급을 진행하고 있다. MyCAD는 크게 MyChip Station Pro, MyAnalog Station, MyLogic Station, MyVHDL Station으로 구성되어 있는 EDA(Electronic Design Automation) Tool이다.

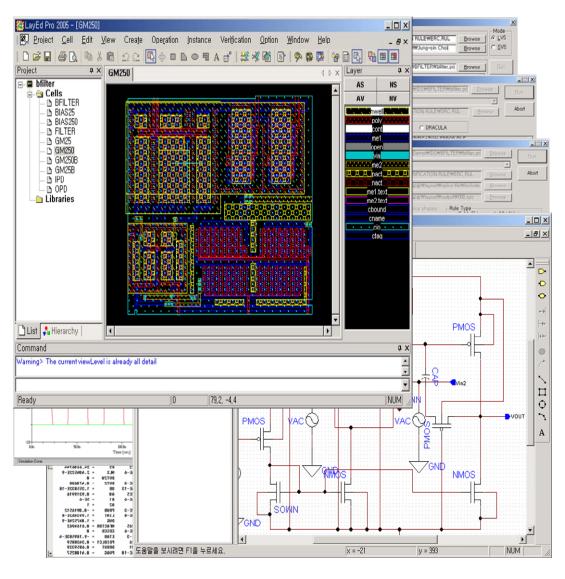

MyCAD의 MyChip Station Pro와 MyAnalog Station은 회로 설계, Netlist 추출, Layout 그리고 검증을 위한 Tool로써 최종 GDS파일로 변환할 수 있다.

MyLogic Station은 front-end 설계용 Tool로써 회로설계(schematic capture), 회로검증(function simulation) 및 EDIF 생성(EDIF netlist generation) 등을 지원한다.

또한 MyCAD는 VHDL 설계, 논리합성 및 최적화, 디지털 논리회로 설계 그리고 모의 실험 등의 작업을 일반 PC Windows상에서 모든 작업을 수행하도록 최적화한 EDA Tool이다.

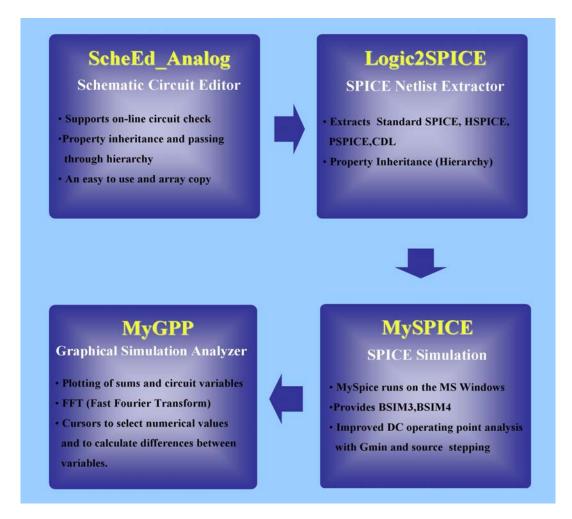

< 그림1.1 MyCAD IC Design Flow >

# 1.1. MyChip Station Pro

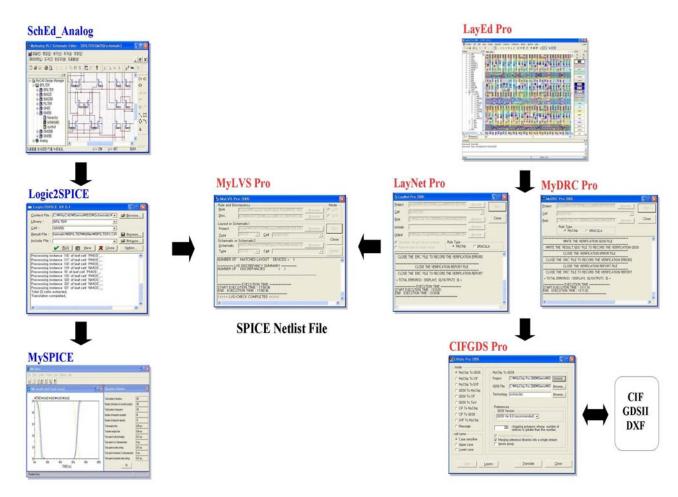

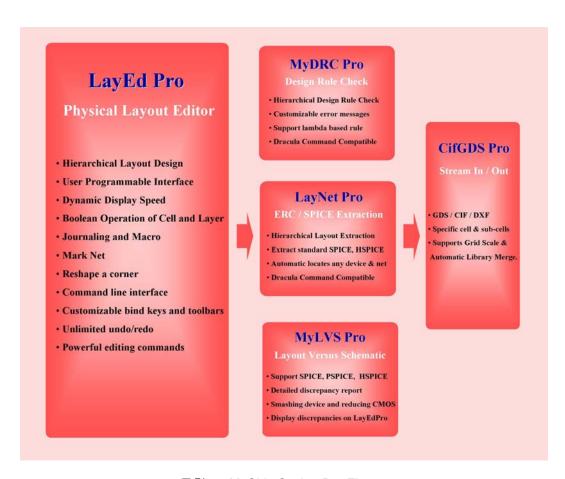

MyChip Station™ Pro는 window에서 workstation과 같이 정교한 physical design을 할 수 있도록 구현한 IC Design Solution이다.

Layout 설계를 위한 LayEd Pro는 Customizable Polygon 기반의 Full custom IC layout 편집기이다. 물리적인 설계 검증에는 Design rule을 검사하는 MyDRC Pro, Layout과 Schematic 의 Netlist를 비교하는 MyLVS Pro, 그리고 Parasitic information 과 Netlist를 추출하는 LayNet Pro등으로 구성된다. 이 러한 Verification Tool은 사용자가 정의한 룰 파일을 사용할 수 있으며 DRACULA™ 와도 호환 할 수 있다.

마지막으로 CifGDS Pro는 규격화된 파일(GDS II, CIF, DXF)을 사용하여 Layout data를 Import, Export 할 수 있다.

현재 국내의 수많은 대학교내 전기, 전자, 통신, 반도체 관련학과에서 MyCAD를 이용한 설계교육을 진행하고 있고, 산업체에서는 IC layout, MEMS Design, LCD 그리고 Optical 등의 관련분야에서 Layout 설계에 사용하고 있다. 국외로는 미국, 일본, 유럽, 중국 그리고 아시아 등의 뛰어난 전문가들로부터 Analog 및 Mixed IC 설계에 수년간 사용되어오고 있으며 뛰어난 성능을 입증 해주고 있다.

< 그림1.2 MyChip Station Pro Flow >

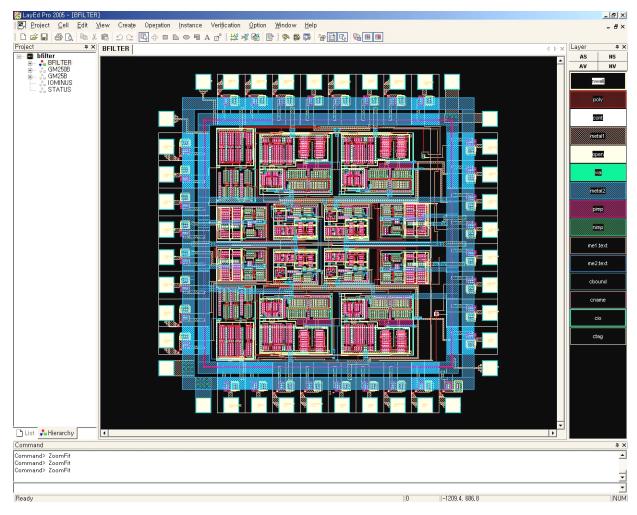

#### (1) LayEd Pro

LayEd Pro는 Layout 편집기로써 파워풀하고 정교한 Polygon기반의 Graphical User Interface를 사용한다. 또한hierarchical Layout 설계가 가능하며 빠른 처리 능력과 예상치 못한 시스템 오류 발생시 자동 복구하는 기능 등 쉽고 편리한 기능들을 제공함으로써 초보자에서 전문가까지 사용할 수 있다.

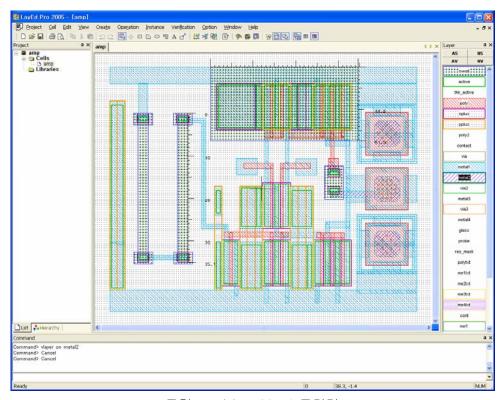

< 그림1.3 LayEd Pro를 이용한 BFILTER 설계 >

# (2) MyDRC Pro

Layout 설계를 한 후 올바르게 설계되었는지를 검증하는 Tool로써 Hierarchical Design Rule 검사를 통하여 rule에 맞지 않는 부분을 display 해준다. Real Time DRC를 제공함으로써 실시간으로 Rule체크도 가능하다. 또한 DRACULA™ 와 호환이 되고 대용량 데이터도 고속으로 체크가 가능하다.

#### (3) LayNet Pro

Layout에서 Netlist를 추출하는 Tool로써 Hierarchical ERC rule Check가 가능하고 SPICE와 HSPICE format에 맞는 Netlist를 추출할 수 있으며 DRACULA™와 호환이 된다.

#### (4) MyLVS Pro

Hierarchical Layout Netlist와 Schematic Netlist의 비교 분석하는 Tool로써 다양한 SPICE Netlist format (standard, SPICE, HSPICE, PSPICE)을 지원한다.

# (5) CifGDS Pro

Industry standard(GDSII, CIF, DXF)를 사용하여 다양한 형식으로 Layout data를 import, export로 변환할 수 있는 Tool로써 industry standard의 Data를 상호 변환한다. 또한 Layer or Cell을 사용자가 선택적으로 변환 하도록 되어 있다.

# 1.2. MyAnalog Station

MyAnalog Station은 Analog 전자회로를 설계하고 이를 모의 실험하는 Tool이다. Schematic editor로 설계한 Data를 Netlist로 변환하는 내부과정을 SPICE-Netlist로 자동 변환하며 생성된 SPICE-Netlist에 추가로 필요한 Line을 추가한 후 MySPICE에서 원하는 Analysis를 선택하여 모의실험 한다. Post Processor(MyGPP)를 사용하면 모의실험 결과가 좀 더 분석하기 쉽고 멋진 리포트로 변경 된다.

< 그림1.4 MyAnalog Station Flow >

# (1) Schematic Editor

제공되는 Analog Library로 쉽게 Schematic 설계를 할 수 있으며 Symbol Editor로 Symbol을 만들어서 사용할 수 있다. 또한 전기적인 특성을 고려하여 설계된 회로를 ERC rule로 검증하여 rule 에 위배되는 Error를 Display해준다.

#### (2) Logic2SPICE

다양한 형식의 SPICE Netlist (Standard SPICE, HSPICE, PSPICE)를 추출할 수 있다.

#### (3) MySPICE

MySPICE는 복잡한 회로를 DC 동작점 계산, 과도 전류, perform Fourier, noise, 왜곡 파형을 분석할 수 있는 analog simulator이다. MS Window에 기초한 GUI를 제공하며 Berkeley SPICE 모델 제공은 기본, 새로운 모델도(BSIM, BSIM2, BSIM3 Losy Trasmission Lines, MOS Level 6) 제공하고 있다.

#### (4) MyGPP

MyGPP는 MySPICE를 좀 더 분석하기 쉽게 하기 위해 합과 차, 미분과 적분 같은 Function, FFT(Fast Fourier Transform), Cursor 기능을 제공한다.

#### ※사용환경

- CPU: Pentium2 이상(최소) / Pentium-4 권장

- RAM: 128MB 이상(최소) /512MB 권장

- HDD: 50MB 이상(최소) / 2GB 여유공간 권장

- OS: Windows 95 이상(최소) / Windows 2000 또는 XP 권장

#### 2. Tutorial 실습 목적 및 예제

#### 2.1.Tutorial 실습 목적

본 Tutorial에서는 Inverter, NAND Gate 그리고 MUX의 Schematic및 Layout의 설계를 하고 검증을 모의실험으로 할 수 있도록 한다. 다음 과정으로 Schematic과 Layout의 설계를 비교 해서 설계한대로 매칭이 되었는지 검증한다. Schematic에서부터 Layout, GDSII파일까지 실행 및 생성하여 IC설계에 대한 전반적인 이해를 돕는데 목적이 있다.

# 2.2.MyCAD Tutorial 실습 환경

- (1) 설계 환경 파일 & 환경 설정

- ① MyAnalog Station

- i. Library File : C:\MyAnalogV63\Schematic\Library\MyAnalog 폴더에 있는 Analog.lib에서 제 공, 실습에 필요한 모든 Cell을 제공

- ii. Include File : C:\MyAnalogV63\Schematic\spice 폴더에서 SCN4M\_SUMB SPICE BSIM3.txt 파일 제공, Spice Simulation시 NMOS와 PMOS의 기본 model 제공 (MOS model과 Spice Netlist 추출 시 MOS의 속성이 같아야 한다.)

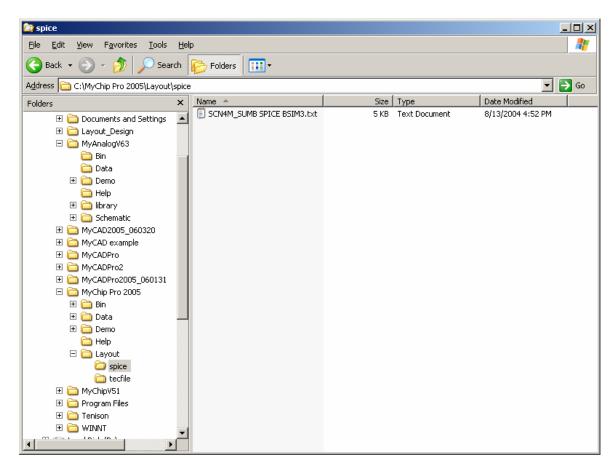

#### 2 MyChip Station Pro

- i. SCMOS\_SCN4ME\_SUBM.TEC : C:\MyChip Station Pro 2005\Layout\tecfile에서 제공, 레이어에 관한 정보와 화면 디스플레이에 관한 정보를 담고 있는 파일

- ii. Stipple.lst : C:\MyChip Station Pro 2005\Layout\tecfile에서 제공, 레이어의 채우기 패턴 모 양을 정의하여 놓은 파일

- iii. SCMOS\_SCN4ME\_SUBM\_DRC.rul:

C:\MyChip Station Pro 2005\Layout\tecfile에서 제공, MyDRC Pro수행을 위한 파일로서, 설계규칙 검증을 위한 파일

iv. SCMOS\_SCN4ME\_SUBM\_ERC.rul:

C:\MyChip Station Pro 2005\Layout\tecfile에서 제공, LayNet Pro, MyLVS Pro수행을 위한 파일로서, Netlist 추출할 때 전기적 소자의 추출에 관한 규칙파일

- v. Include File:

- C:\MyChip Station Pro 2005\Layout\Spice폴더에서 SCN4M\_SUMB\_SPICE \_BSIM3.txt파일 제공, Spice Simulation시 NMOS와 PMOS의 기본 model 제공

- vi. SCMOS\_SCN4ME\_SUBM의 파일들은 VLSI circuit 회사인 MOSIS사에서 만든 설계규칙 이다. Transistor의 크기는 (W/L)p = (2.4/0.4)㎞, (W/L)n = (1.2/0.4)㎞를 사용한다.

#### ③ 실습환경

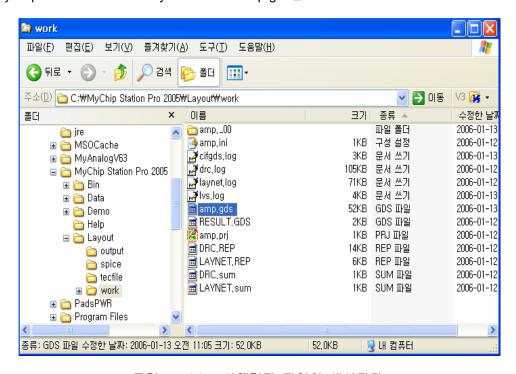

※ 먼저 실습하기 전 설계 시 편의를 위해 그림과 같이 폴더를 생성하고 각각의 폴더 안에 파일들을 넣는다.

< 그림2.2.(1)-1 실습에 필요한 폴더생성 및 파일 위치지정 >

■<그림2.3.(1)-1>과 같이 하위폴더를 만들고 다음의 파일들을 각각의 폴더 안에 넣는다.

#### -C:₩MyChip Pro 2005₩Layout 폴더

- SPICE file 폴더: SCN4M\_SUMB SPICE BSIM3.txt

SCMOS\_SCN4ME\_SUBM\_DRC.rul,

SCMOS\_SCN4ME\_SUBM\_ERC.rul,

SCMOS\_SCN4ME\_SUBM\_ERC(nwell).rul (APPENDIX B.3.을 메모장

에 복사하여 만든다.)

#### -C:₩MyAnalogV63₩Schematic 폴더

- Library 폴더 : C:\MyAnalogV63\Library\MyAnalog 폴더 전부 복사

- SPICE file 폴더: SCN4M\_SUMB SPICE BSIM3.txt

# ④ 중요 File 설명

| 확장자명         |         | 내 <del>용</del>                                                                                          |  |  |

|--------------|---------|---------------------------------------------------------------------------------------------------------|--|--|

| *.TEC        |         | MyChip Station에서 사용하는 Technology 파일이다. 사용자는 이 파일을 원하는 공정에 맞추어서 변경 사용할 수 있다.                             |  |  |

| *            | .LST    | 라이브러리 작업에 사용할 layer fill 패턴 정보를 담고 있는 파일이다. 사용자가 변경 가능하다.                                               |  |  |

|              | DRC.rul | Design 설계 오류 검색 시 그 기준이 되는 파일을 의미한다. MyDRC Pro 실행 시 이 파일을 기준으로 하여 rule체크를 한다.                           |  |  |

| *.rul        | ERC.rul | 전기적 오류 검색과 설계 회로 Netlist 추출에 필요한 Device들과 net 정보를 가지고 있다. LayNetPro 사용시 이 파일을 기준으로 하여 Rule체크를 한다.       |  |  |

| *.cir, *.spc |         | SPICE 형태의 Netlist 추출 시 결과 파일로, 회로의 연결 정보를 담고 있는 파일이다                                                    |  |  |

| *.dis        |         | MyLVSPro 실행 후 Layout과 Schematic의 비교 분석결과 정보를 담고 있는 파일로 Discrepancy 내용을 확인할 수 있다.                        |  |  |

| *.inc        |         | SPICE Simulation에 사용할 model parameter를 담고 있는 파일이다. MyCAD Tutorial에서는 TSMC 0.35um공정 model parameter제공한다. |  |  |

# (2) 설계 후 생성되는 파일

Schematic 설계와 Layout 설계를 하면 여러 가지 파일이 생성되는데 파일들의 역할은 다음과 같다.

| 구 분         | 파 일 명      | 내 용                                                                                   |

|-------------|------------|---------------------------------------------------------------------------------------|

|             | schematic  | Schematic 생성할 때 inv 폴더에 만들어짐                                                          |

|             | symbol     | symbol 생성할 때 inv 폴더에 만들어짐                                                             |

| MyAnalog    | netlist    | Netlist 추출에 관한 정보가 담긴 파일                                                              |

| Station     | *.mdc      | Schematic 실행파일                                                                        |

|             | *.lib      | 설계 후 저장하면 생성되는 정보파일                                                                   |

|             | *.log      | Simulation 시 발생한 error메시지를 담고 있는 파일                                                   |

|             | layout.1   | 셀에서 만든 레이아웃 데이터                                                                       |

|             | drc_bin.1  | DRC 수행결과의 오류를 담고 있으며 그래픽 정보를 제공                                                       |

|             | drc.1      | DRC 수행결과의 오류를 담고 있으며 텍스트파일의 형식으로 오류가 발생한 부분의 XY 좌표를 제공                                |

| MyChip      | extract.1  | Extraction 수행결과 파일로서 레이아웃이 담고 있는 소자와 연<br>결 상태에 관한 정보 수록                              |

| Station Pro | devshape.1 | Extraction 수행 결과 생기며, LayEd Pro에서 Find Device 명령을<br>통해 레이아웃 상에서 원하는 소자를 찾을 수 있는 정보제공 |

|             | netshape.1 | Extraction 수행결과 파일로 소자연결 네트에 관한 정보를 담고<br>있는 파일                                       |

|             | erc_bin.1  | ERC 수행결과를 담고 있는 파일                                                                    |

|             | lvs_bin.1  | LVS 수행결과 스케메틱과 레이아웃이 일치하지 않은 오류에 관한 정보                                                |

# 2.3. Two stage amp 이론

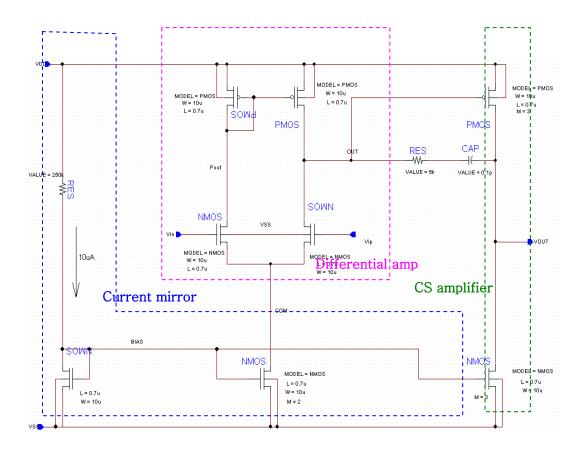

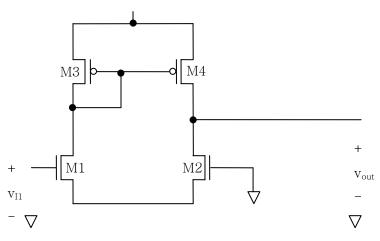

#### (1) Schematic

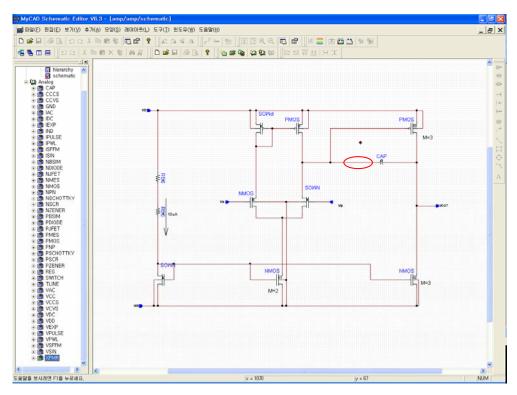

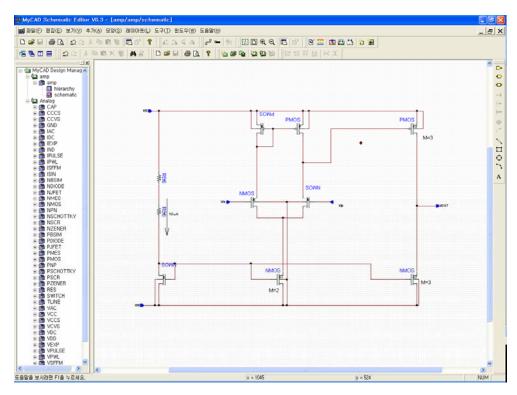

<그림 2.3.(1)-1 schematic of the two stage amp>

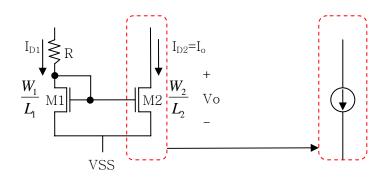

#### (2) Current mirror

① 개요

다음과 같은 간단한 current mirror 회로의 동작 특성에 대해서 알아본다.

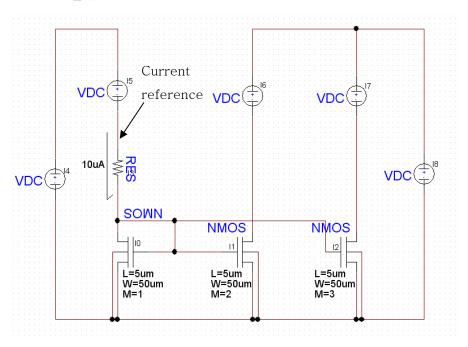

<그림 2.3.(2)-1 basic current mirror schematic>

그림 2.3.(2)-1은 기본적인 current mirror 이다. M1, M2에 흐르는 전류는 아래의 식을 이용하여 구할 수 있다.

$$I_{D1} = \frac{\beta_1}{2} \cdot (V_{GS1} - V_{THN})^2 \tag{2.1}$$

$$I_{D2} = \frac{\beta_2}{2} \cdot (V_{GS2} - V_{THN})^2 \tag{2.2}$$

$V_{GS1}$ = $V_{GS2}$  이므로, drain 전류의 비를 구하면

$$\frac{I_{D2}}{I_{D1}} = \frac{\frac{W_2}{L_2}}{\frac{W_1}{L_1}} = \frac{W_2 L_1}{W_1 L_2} = \frac{\beta_2}{\beta_1}$$

(2.3)

그림 2.3.(2)-1에서 전류  $I_{D1}$ 은 다음과 같이 구할 수 있다.

$$I_{D1} = \frac{VDD - V_{GS} - VSS}{R} = \frac{KP \cdot W_1}{2L_1} \cdot (V_{GS1} - V_{THN})^2$$

(2.4)

current source의 출력저항은 M2의 출력저항이므로

$$r_{o2} = \frac{1}{\lambda I_o} = \frac{1}{\lambda I_{D2}} \tag{2.5}$$

#### ② 예제 (current mirror simulation)

#### i. 전류원의 설계

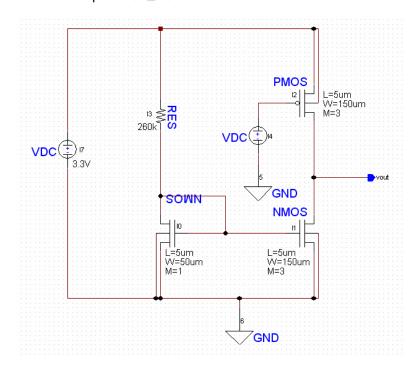

<그림 2.3.(2)-2 current mirror의 schematic>

current reference 회로에 10uA가 되도록 설계

10 → L=5um, W=50um, \*M=1

I1 → L=5um, W=50um, \*M=2

$12 \rightarrow L=5um, W=50um, *M=3$

\*M (multiplier): W의 크기를 M상수만큼 곱함

ex) L = 5um, W = 5um, M = 3

$$\rightarrow$$

L = 5um, W=5um x 3 = 15um

MOS IO의 V<sub>GS</sub>는

$$I_D = \frac{\beta}{2} \cdot (V_{GS} - V_{THN})^2 = \frac{KPn}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{THN})^2$$

$$V_{GS} = \sqrt{\frac{2I_D \cdot L}{KP_n \cdot W}} + V_{THN} = \sqrt{\frac{2 \times 10uA \times 5um}{50uA/V_2 \cdot 50um}} + 0.502 = 0.702[V]$$

저항 R 값을 결정하면

$$R = \frac{VDD - V_{GS} - VSS}{I_D} = \frac{3.3V - 0.702 - 0}{10uA} = 259.8[k\Omega] \approx 260[k\Omega]$$

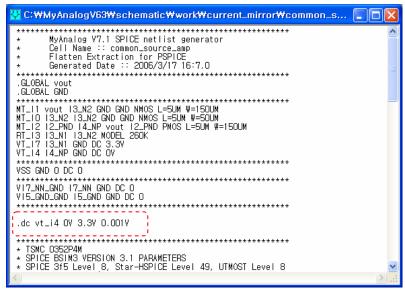

ii. Current mirror schematic으로부터 추출된 netlist

<그림 2.3.(2)-3 추출된 netslilt>

# 붉은색 부분을 추가

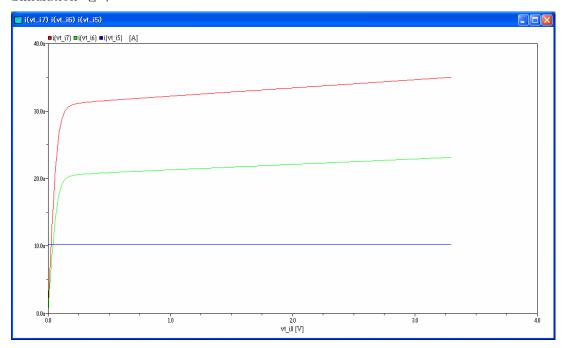

# iii. Simulation 결과

<그림 2.3.(2)-4 current mirror의 동작특성>

# (3) Differential amplifier

# ① 개요

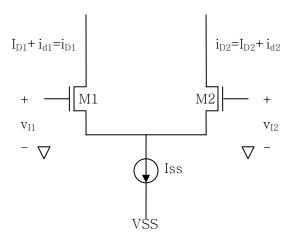

<그림 2.3.(3)-1 Differential amp>

AC성분과 DC성분이 합쳐진 M1, M2의 source 전류는 다음과 같다.

$$I_{SS} = i_{D1} + i_{D2} \tag{3.1}$$

M1, M2 gate의 입력전압은

$$v_{DI} = v_{I1} - v_{I2} = V_{GS1} + v_{gs1} - V_{GS2} - v_{gs2}$$

(3.2)

(V<sub>GS1</sub>, V<sub>GS2</sub> → 전압의 DC 성분, v<sub>gs1</sub>, v<sub>gs2</sub> → 전압의 AC 성분)

차동 입력전압의 크기는 아래의 식과 같이 나타낼 수 있다.

$$v_{DI} = \sqrt{\frac{\beta}{2}} (\sqrt{i_{D1}} - \sqrt{i_{D2}})^2$$

(3.3)

차동 증폭기의 차동 입력시에 허용 가능한 최대 입력전압의 크기는 아래와 같다.

$$v_{DIMAX} = \sqrt{\frac{2I_{SS}}{\beta}} \tag{3.4}$$

$$v_{DIMIN} = -\sqrt{\frac{2I_{SS}}{\beta}} \tag{3.5}$$

차동 증폭기의 공통모드 입력시에 허용 가능한 최대 입력전압의 크기

<그림 2.3.(3)-2 공통모드 입력범위를 결정하기 위한 차동증폭기>

$$v_{IMIN} = \sqrt{\frac{I_{SS}}{\beta_1}} + V_{THN} + \sqrt{\frac{2I_{SS}}{\beta_6}} + VSS$$

(3.6)

$$v_{IMAX} = VDD - \left[ \sqrt{\frac{I_{SS}}{\beta_3}} + V_{THP} \right] + V_{THN}$$

(3.7)

<그림 2.3.(3)-3 AC mode에서의 차동 증폭기>

차동 증폭기의 전압이득은 아래와 같다.

$$A_{v} = \frac{v_{out}}{v_{i1}} = \frac{v_{out}}{v_{i1} - v_{i2}} = g_{m}(r_{o2} \parallel r_{o4})$$

(3.8)

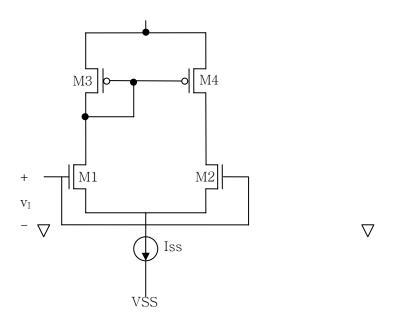

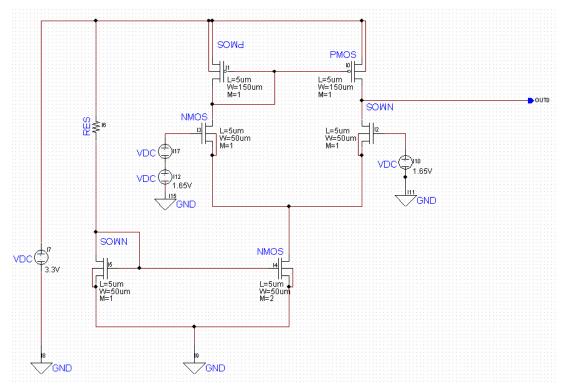

# ② 예제 (differential amp simulation)

# i. Differential amplifier의 설계

<그림 2.3.(3)-4 differential amplifier의 schematic>

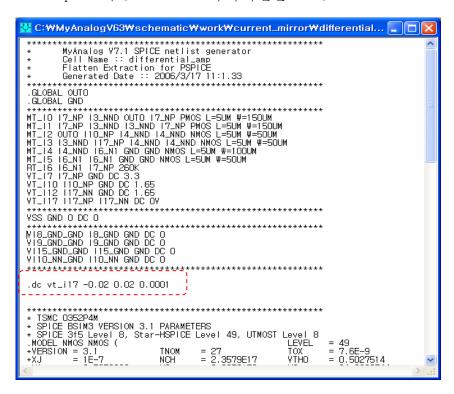

ii. Differential amplifier의 schematic으로부터 추출된 netlist

<2.3.(3)-5 추출된 netlist>

위의 simulation은 차동 증폭기의 DC 특성을 보기 위해서 붉은색 부분을 추가하였다. (차동 입력의 DC 전압을 -0.02V~+0.02V까지 증가시킴)

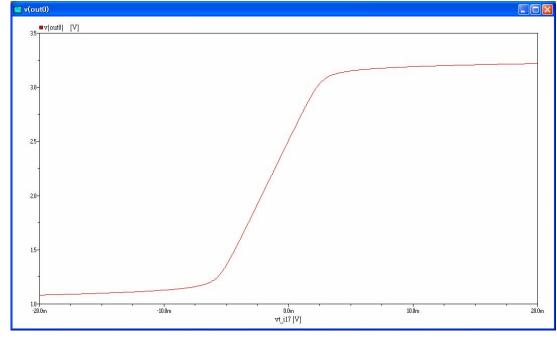

#### iii. Simulation 결과

a. DC 입력일 때의 출력화형(DC 입력 전압을 0.02V ~ 0.02V까지 변화시킴)

<2.3.(3)-6 차동 증폭기의 DC 특성>

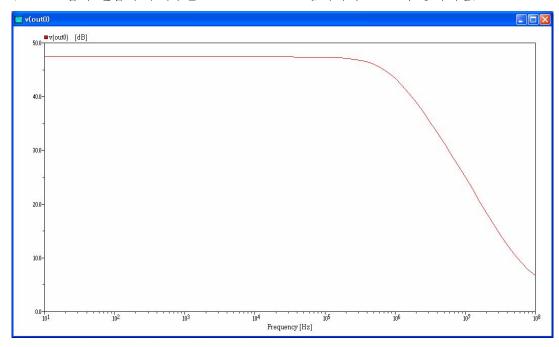

# b. AC 입력일 때의 출력파형

(AC 1V 입력 전압의 주파수를 10Hz ~ 100Mhz범위에서 10Hz씩 증가시킴)

<2.3.(3)-7 주파수에 따른 전압이득 특성>

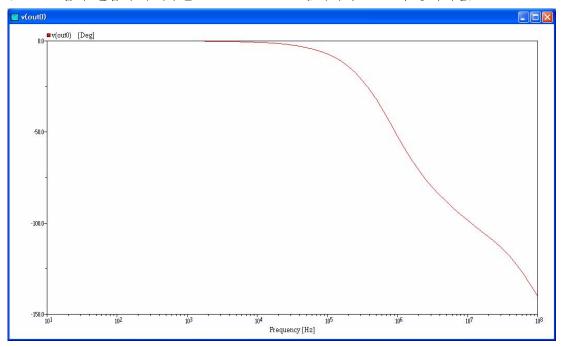

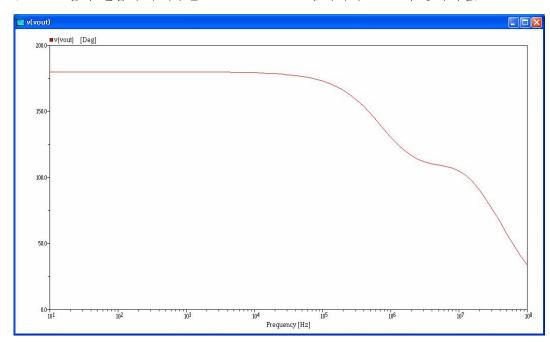

# C. AC 입력일 때의 Phase

(AC 1V 입력 전압의 주파수를 10Hz ~ 100Mhz범위에서 10Hz씩 증가시킴)

<2.3.(3)-8 주파수에 따른 phase 특성>

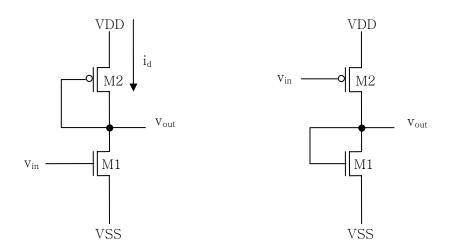

# (4) Common source amplifier

① 개요

<그림 2.4.(4)-1 Common source amplifier>

왼쪽 common source amplifier의 소신호 전압 이득은 아래와 같다.

$$\frac{v_{out}}{v_{in}} = \frac{i_d \cdot \frac{1}{g_{m2}}}{i_d \cdot \frac{1}{g_{m1}}} = -\frac{\frac{1}{g_{m2}}}{\frac{1}{g_{m1}}} = -\frac{\text{resistance in the drain}}{\text{resistance in the source}} = -\frac{g_{m1}}{g_{m2}}$$

(4.1)

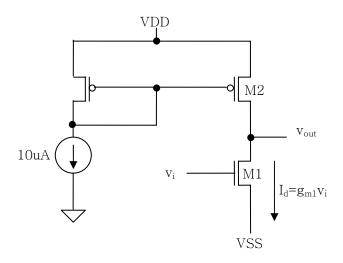

<그림 2.4.(4)-2 전류원 부하를 갖는 common source amplifier>

증폭기에서 current source 부하는 CMOS 공정에서 가장 큰 저항을 제공한다.

그림 2.4.(4)-1은 current source 부하를 가진 common source 증폭기이다. M1이 증폭기의 common source 부분이고, M2는 current source 부하이다.

common source 증폭기의 전압이득을 구하면

$$A_{v} = \frac{v_{o}}{v_{i}} = -\frac{r_{o1} \parallel r_{o2}}{\frac{1}{g_{m1}}} = -\frac{g_{m1}}{g_{o1} + g_{o2}} \qquad \left(\Theta \ r_{o} = \frac{1}{\lambda I_{D}}\right)$$

(4.2)

- ② 예제 (common source amplifier simulation)

- i. Common source amplifier의 설계

<그림 2.4.(4)-3 common source amplifier의 schematic>

ii. Common source amplifier의 schematic으로부터 추출된 netlist

<그림 2.4.(4)-4 추출된 netslit>

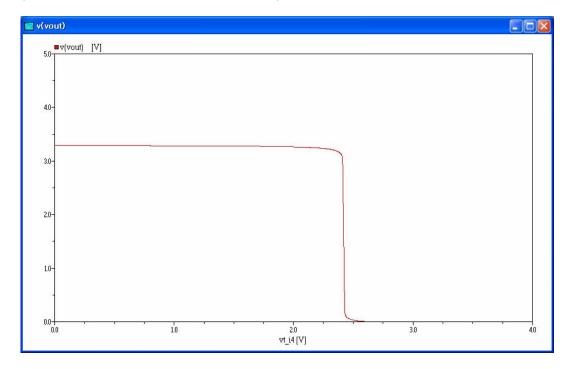

# iii. Simulation 결과

a. DC 입력일 때의 출력파형

(DC 입력 전압을 0V~3.3V까지 증가시킴)

<2.4.(4)-5 common source 증폭기의 DC 특성>

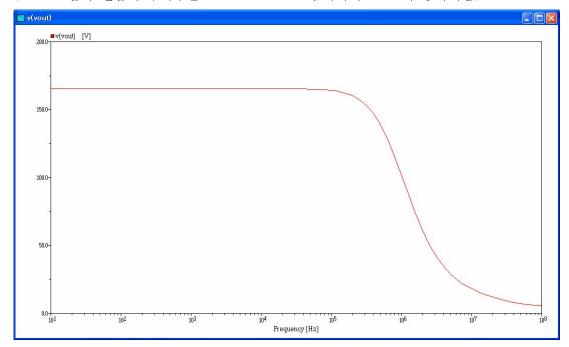

b. AC 입력일 때의 출력파형

(AC 1V 입력 전압의 주파수를 10Hz ~ 100Mhz범위에서 10Hz씩 증가시킴)

<2.4.(4)-6 주파수에 따른 전압이득 특성>

# C. AC 입력일 때의 출력파형

(AC 1V 입력 전압의 주파수를 10Hz ~ 100Mhz범위에서 10Hz씩 증가시킴)

<그림 2.4.(4)-7 주파수에 따른 phase 특성>

# 2.4.Two stage amp 설계

(1) Two stage amp 설계

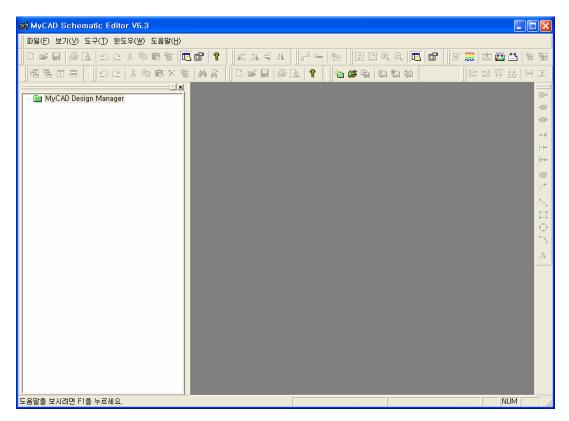

MyCAD Pro → Schematic Editor for MyAnalog를 실행 시킨다.

<그림 2.3(1)-1 Schematic Editor>

#### ① Library 생성

i. New Folder

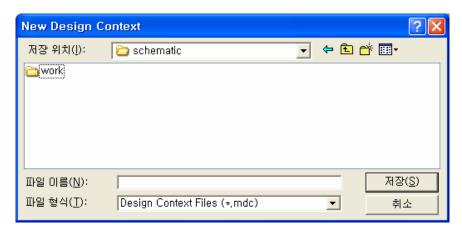

menu → 파일 → 새 디자인 열기 선택 후 C:\MyAnalogV63\Schematic\에 새로운Work Folder를 만든다.

<그림 2.3(1)-2 New Design Context>

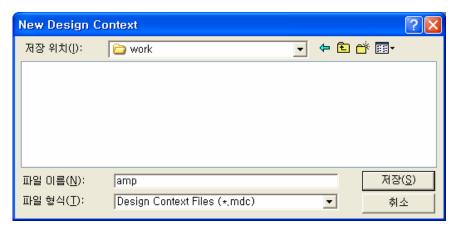

#### ii. New Library file

Work Folder를 만든 후 파일이름을 amp로 정해준다. MDC file (MyCAD Design Context)을 만들면 Library file 도 생성된다. 확장자명은 생략해도 자동으로 만들어진다.

<그림 2.3(1)-3 실행파일 만들기>

저장을 한 후 `새로운 라이브러리를 만들겠습니까?' 에서 확인을 누르면 Library file이 만들어진다.

<그림 2.3(1)-4Library 생성>

#### iii. New Cell & View

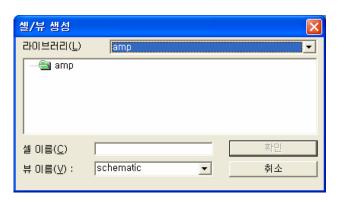

Menu → 파일 → 셀/뷰 만들기 선택 후 셀/뷰 생성 창에서 셀 이름에 amp를 쓰고 뷰 이름에 Schematic을 선택한다.

<그림 2.3(1)-5 Cell 만들기>

<그림 2.3(1)-6 Cell 만들기>

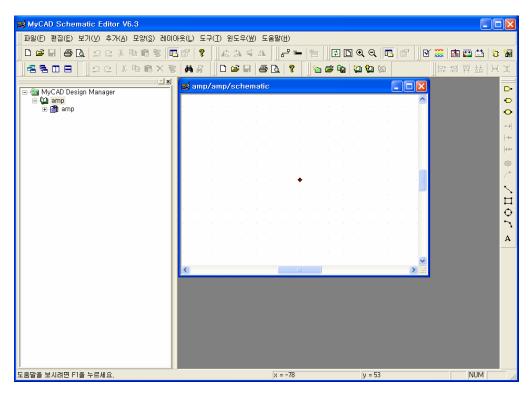

셀/뷰 생성 창에 확인을 누르면 Schematic창이 뜬다.

<그림 2.3(1)-7 Cell 생성>

#### iv. Add Library

설계를 간편하게 하기 위해 제작되어 있는 심볼을 불러와서 쓴다.

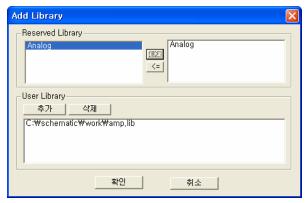

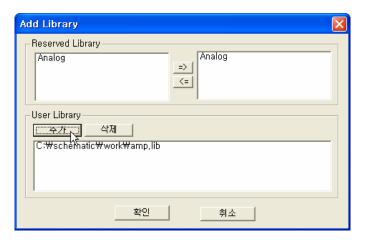

Menu → 파일 → 라이브러리 추가/삭제를 선택하면 Add Library창이 뜬다. Reserved Library창의 Analog를 선택하고 중앙에 있는 오른쪽 화살표를 누른다.

<그림 2.3(1)-8 Library 추가>

<그림 2.3(1)-9 Library 추가>

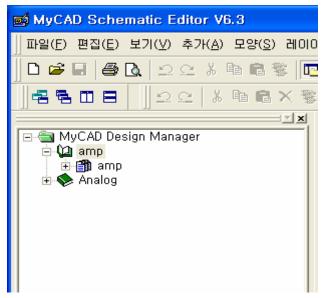

Add Library창의 확인을 누르면 Analog Library가 추가된다.

<그림 2.3(1)-10 추가된 Library>

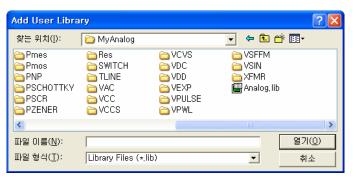

Reserved Library에 Analog가 없으면 User Library의 추가를 누른 후 C:\MyAnalogV63 \Library\MyAnalog\Analog.lib를 선택하고 열기를 누른다.

<그림 2.3(1)-11 Analog Library 추가>

<그림 2.3(1)-12 Analog Library file>

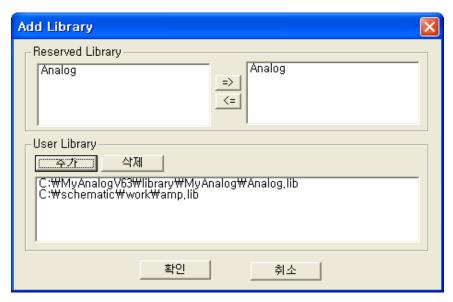

Add Library창에서 확인을 누르면 Analog Library가 추가된다.

<그림 2.3(1)-13 Analog Library 추가>

#### Schematic 설계

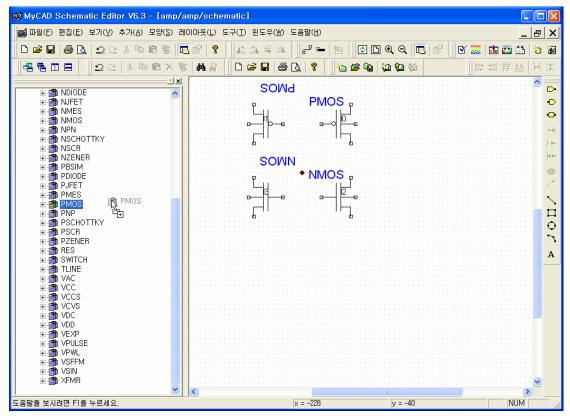

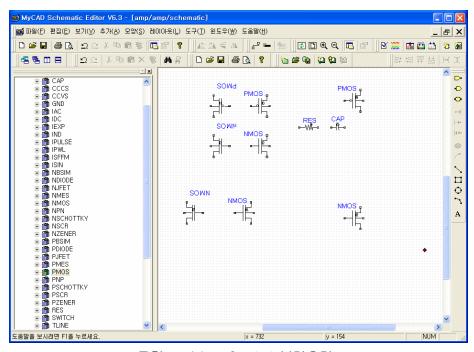

i. Symbol구성

amp를 설계하는데 필요한 symbol(NMOS, PMOS, CAP, VDD, GND, RES)들을 Analog Library에서 끌어서 Schematic창에 놓는다.

<그림 2.3(1)-14 Symbol 불러오기>

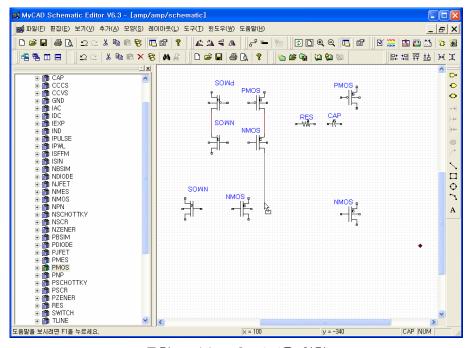

필요한 모든 symbol을 끌어서 Two stage amp를 만들기 위해 자리를 배치한다. 입력포트와 아웃포트는 Object bar에서 끌어 놓는다.

<그림 2.3(1)-15 Symbol 불러오기 >

### ii. 선 연결하기

Symbol의 net point에 더블 클릭한 후에 끌어서 다른 symbol의 net point에 연결시킨다.

<그림 2.3(1)-16 Symbol을 연결>

각 symbol을 연결하여 Inverter회로를 완성시킨다.

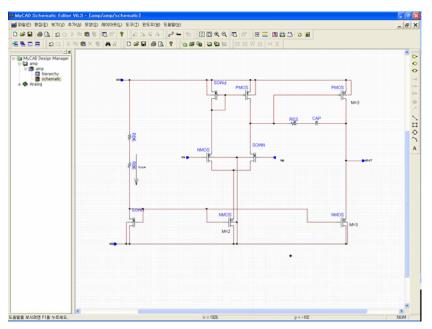

<그림 2.3(1)-17 완성된 Schematic>

# iii. Symbol 속성 설정

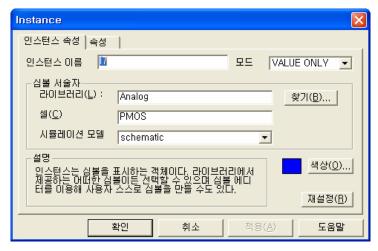

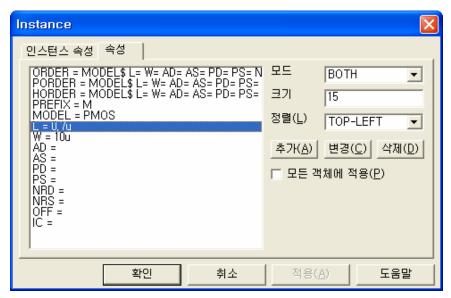

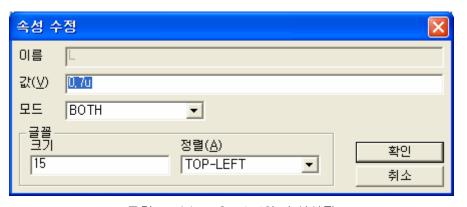

제공된 symbol에는 속성이 비워져 있다. Simulation을 하기 위해서는 매개 변수 값을 정해주어야 한다. PMOS의 symbol의 중앙을 더블 클릭하면 Instance창이 뜬다.

<그림 2.3(1)-18 Symbol의 속성설정>

속성메뉴를 선택하고

<그림 2.3(1)-19 Symbol의 속성설정>

L= 을 더블 클릭하면 속성 수정 창이 뜬다.

<그림 2.3(1)-20 Symbol의 속성설정>

값으로 0.4u를 넣고 확인을 누른다.

이와 같은 방법으로 각각의 symbol들에 대해서 값들을 모두 넣어준다. 작업이 완료되면 저장한다.

#### ③ Schematic 검증

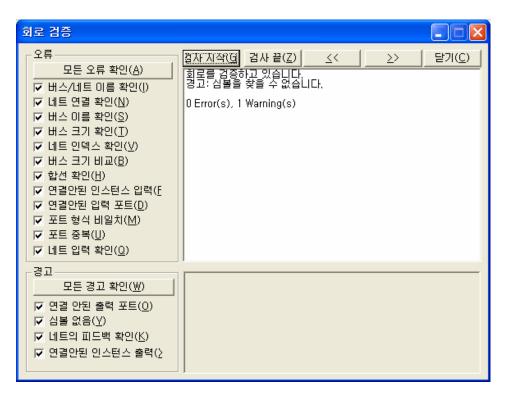

i. ERC (Electric Design Rule Check)

Menu → 도구 → 회로검증 선택한 후 회로검증창의 오류메뉴의 모든 오류 확인을 누르고 경고메뉴의 모든 경고 확인을 선택하고 검사시작을 누른다.

<그림 2.3(1)-21 회로 검증>

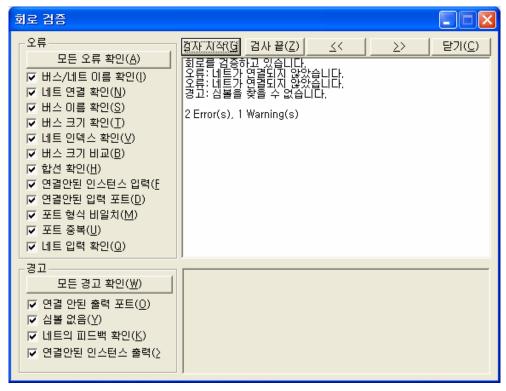

#### ii. Error & Warning

만약 회로에 문제가 발생하면 메시지가 뜬다.

<그림 2.3(1)-22 회로 검증결과>

오류메시지를 보고 수정한다.

#### ④ Netlist 파일 추출

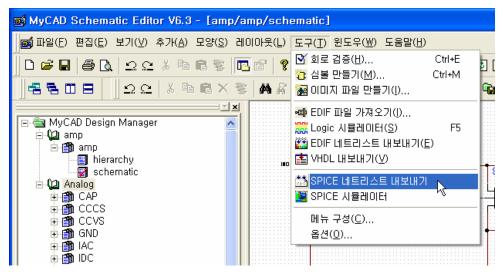

Menu → 도구 → SPICE 네트리스트 내보내기를 선택한다.

i. New folder

<그림 2.3(1)-23 Netlist 추출>

<그림 2.3(1)-24 Netlist 추출>

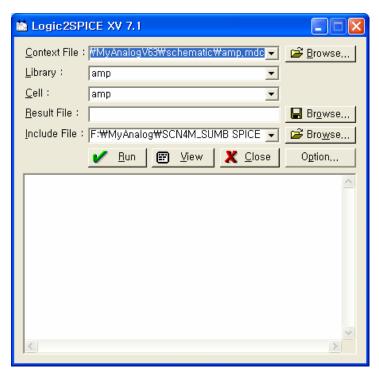

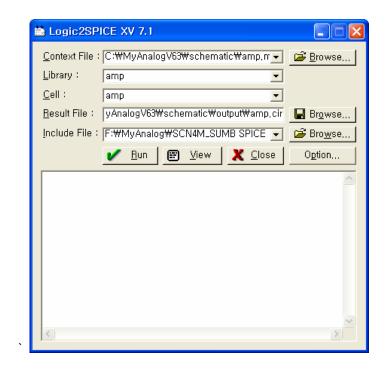

Logic2SPICE창에서 Result File의 오른쪽에 있는 Browse를 선택한다.

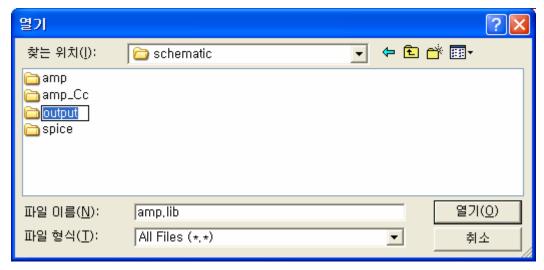

C:\MyAnalogV63\Schematic에 output folder를 만든다.

<그림 2.3(1)-25 output 폴더 생성>

#### ii. New File

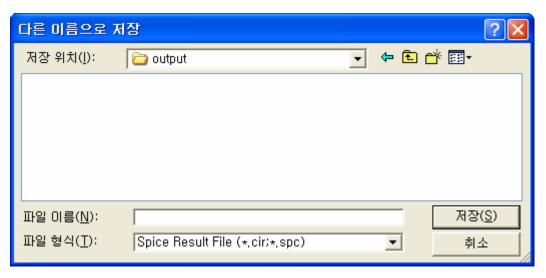

output folder에 파일이름 amp를 만들고 저장한다.

<그림 2.3(1)-26 Netlist 파일 생성>

#### iii. Include file 포함

C:\MyAnalogV63\Schematic\spice file에 있는 SCN4M\_SUMB SPICE BSIM3.txt파일을 Logic2SPICE창의 Include file에 포함시킨다.

<그림 2.3(1)-27 include 파일 포함>

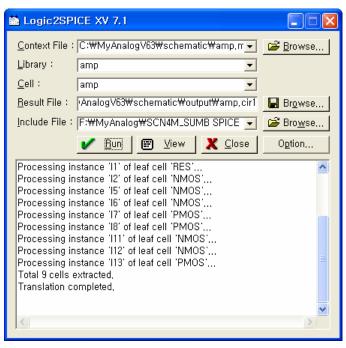

Logic2SPICE창의 RUN을 누르면 Netlist가 생성된다. (output folder에 amp.cir파일이 생성된다.)

<그림 2.3(1)-28 Netlist 생성 완료>

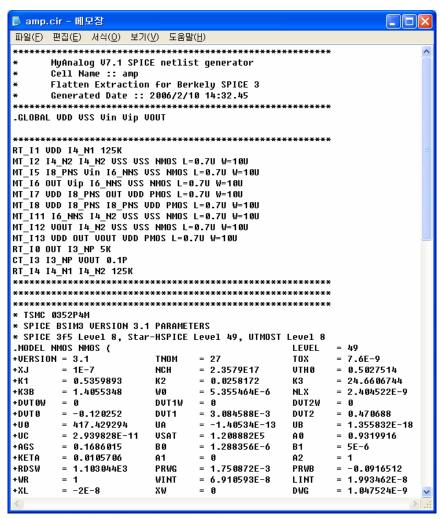

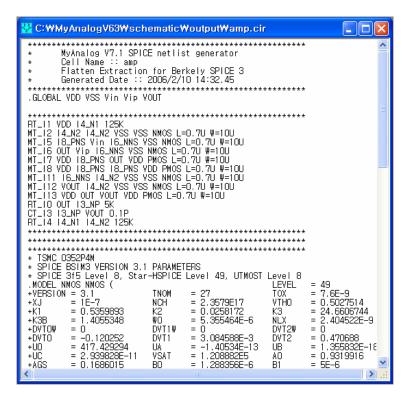

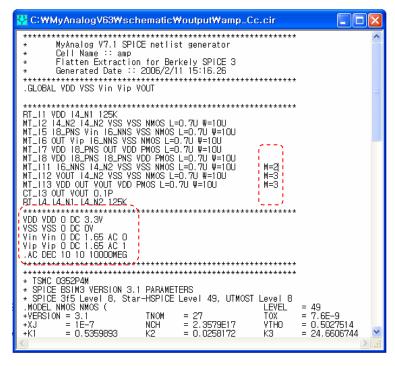

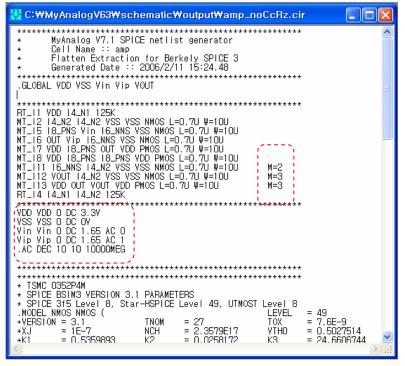

Logic2SPICE창의 View를 누르면 추출된 Netlist를 메모장으로 볼 수 있다.

<그림 2.3(1)-29 추출된 Netlist>

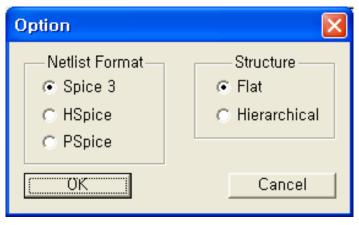

#### iv. Option

Logic2SPICE 창의 Option을 선택하면 Netlist format의 종류(Spice3, HSpice, PSpice)를 정할 수 있고, Structure (flat, Hierarchical)를 구분할 수 있다.

<그림 2.3(1)-30 Netlist 포멧을 위한 옵션>

#### Simulation

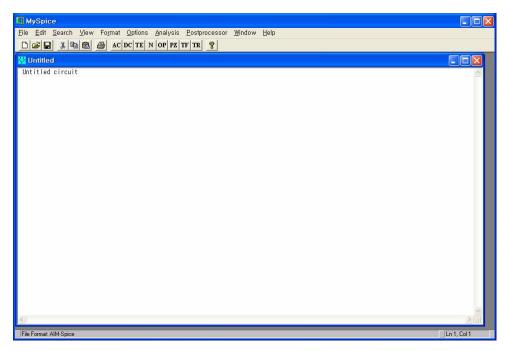

i. MySPICE

시작 → 프로그램 → MyAnalogV63 → MySPICE를 실행시킨다.

<그림 2.3(1)-31 MySpice 실행>

ii. Menu → File → Open 선택 후 C:\MyAnalogV63\Schematic\output의 amp.cir 파일을 선택하고 열기를 누른다.

<그림 2.3(1)-32 amp.cir file 열기>

<그림 2.3(1)-33 amp.cir>

iii. 추출된 Netlist파일에 붉은색 부분을 직접 입력한다. 이것인 simulation을 위한 값들을 지정하는 것이다.

<그림 2.3(1)-34 amp.cir에서 추가된 내용>

iv. Menu → Analysis → Run Standard Spice file을 선택한다. Netlist에 error가 있으면 Run Standard Spice file이 활성화 되지 않는다.

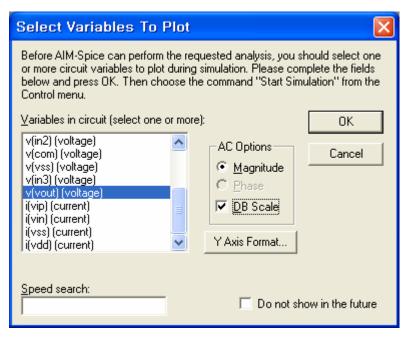

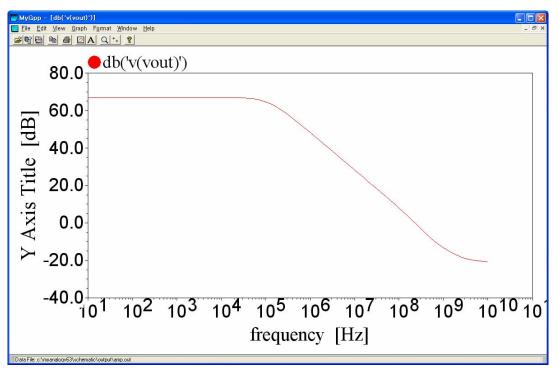

<그림 2.3(1)-35 출력할 plot을 선택>

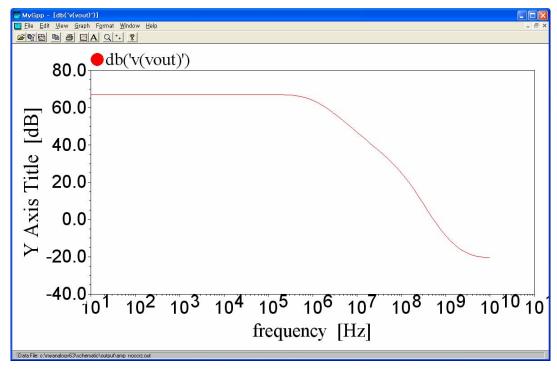

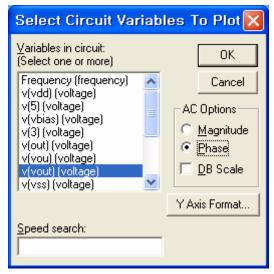

Select Variables To Plot창에서 원하는 결과를 선택한다. v[vout][voltage]를 선택한다. 또한 AC Option에서 Magnitude를 선택하고, DB Scale에 체크하고 OK를 누른다.

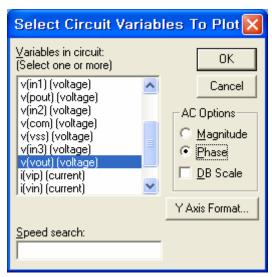

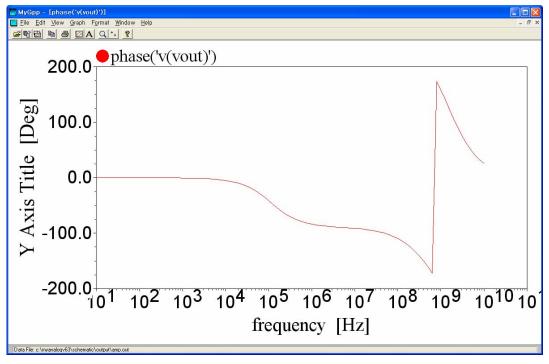

v. Menu → Analysis → Run Standard Spice file을 다시 선택한다.

<그림 2.3(1)-36 출력할 plot을 선택>

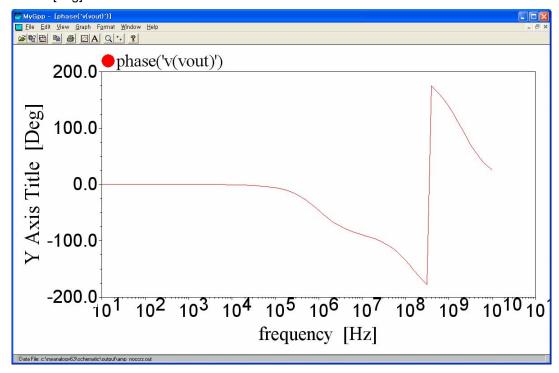

vi. Select Variables To Plot 창에서 원하는 iv에서와 같이 원하는 결과를 선택한다. V[vout][voltage]를 선택한다. 또한 AC Option에서 Phase를 선택하고, OK를 누른다.

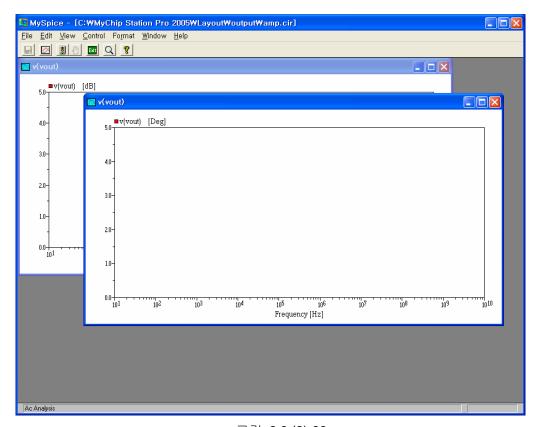

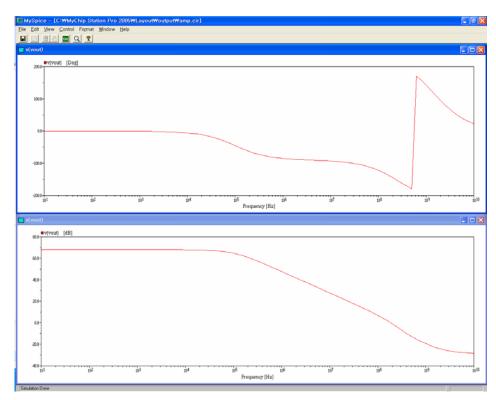

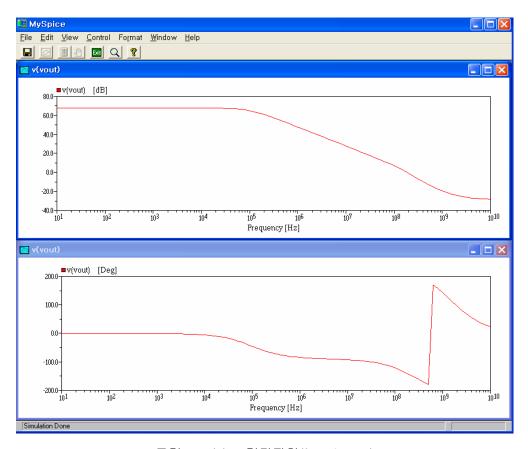

<그림 2.3(1)-37 시뮬레이션 실행 결과>

위와 같이 두개의 창이 나타난다.

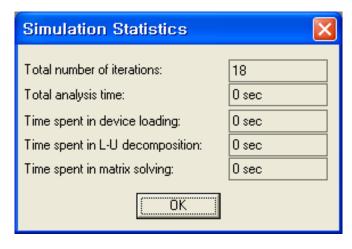

vii. 위의 그림에서 Menu → Control → Start Simulation을 선택한다. Simulation Statistics창에서 상태를 확인하고 OK를 누른다.

<그림 2.3(1)-38 시뮬레이션 결과 창>

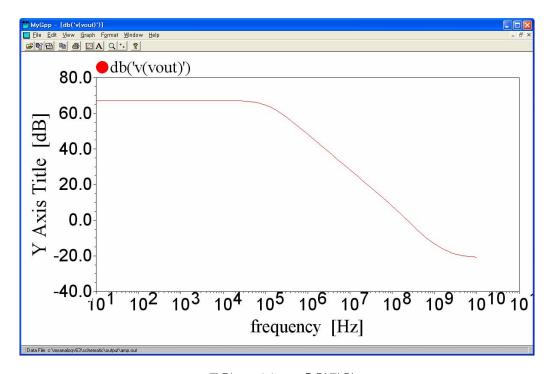

## viii. 결과 확인 (Both Cc & Rz → Stable)

#### a. Magnitude [dB]

<그림 2.3(1)-39 출력파형>

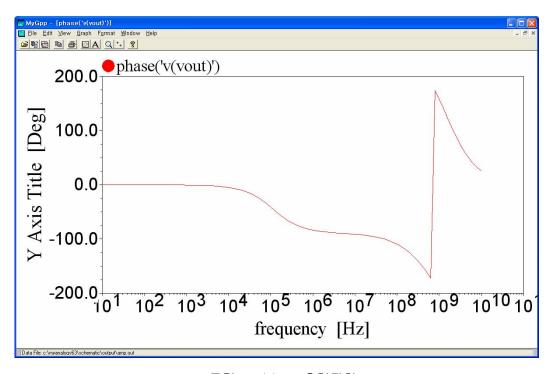

#### b. Phase [deg]

<그림 2.3(1)-40 출력파형>

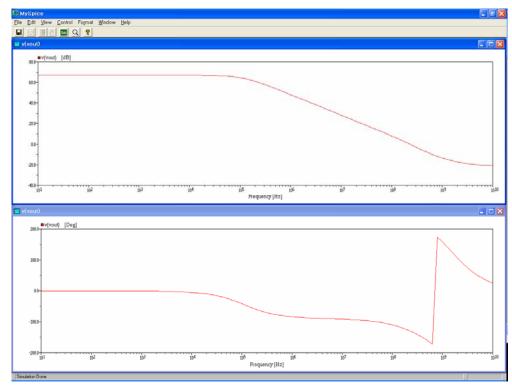

#### ix. 결과확인 (only Cc → unstable)

#### a. Schematic

<그림 2.3(1)-41 Rz가 제거된 회로 >

#### b. Netlist

붉은색 부분을 입력해준다.

<그림 2.3(1)-42 추출된 Netlist>

#### c. Magnitude [dB]

<그림 2.3(1)-43 출력파형>

## d. Phase [deg]

<그림 2.3(1)-44 출력파형>

#### x. 결과확인 without Cc & Rz

#### a. Schematic

<그림 2.3(1)-45 Cc, Rz가 제거된 회로>

#### b. Netlist

붉은색 부분을 직접 입력한다.

<그림 2.3(1)-46 추출된 Netlist>

#### c. Magnitude [dB]

<그림 2.3(1)-47 출력파형>

# d. Phase [deg]

<그림 2.3(1)-48 출력파형>

## (2) Amp Layout 설계

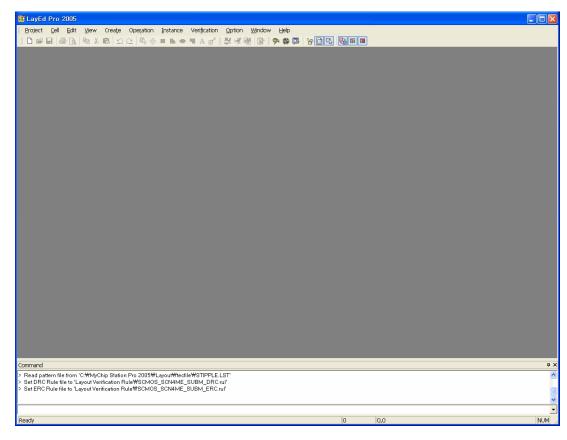

MyChip Station Pro의 LayEd Pro (Layout Editor)를 실행 시킨다.

<그림 2.3(2)-1 LayEd Pro 실행>

# ① Project 생성

i. New Folder

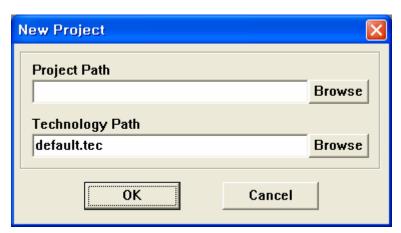

Menu → Project → New Project를 선택한다.

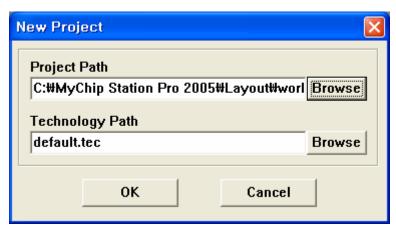

<그림 2.3(2)-2 Project 생성>

New Project창에서 Project Path의 Browse를 선택하고 C:\MyChip Station Pro 2005\Layout 에 work Folder를 만든다.

<그림 2.3(2)-3 work directory 생성>

## ii. New Project & Technology File 변경

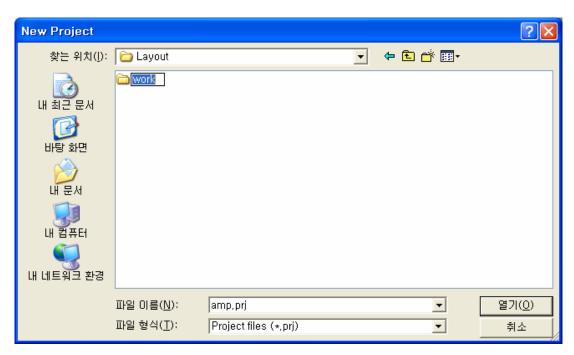

Work Folder에 파일이름에 amp를 쓰고 열기를 누른다. 확장자명(\*.prj)는 자동으로 생성된다.

<그림 2.3(2)-4 프로젝트 생성>

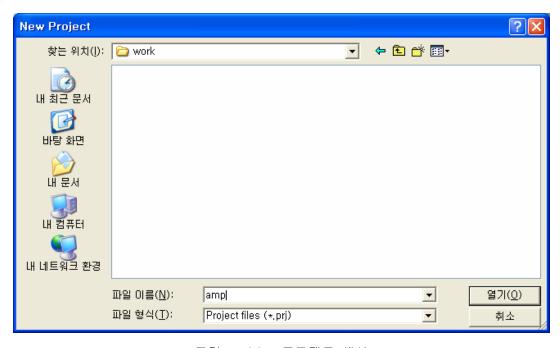

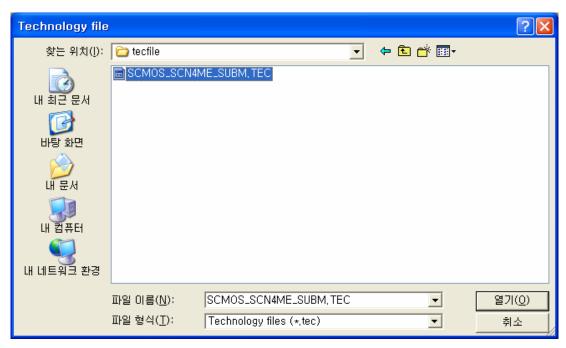

다시 New Project창의 Technology Path의 Browse를 선택한다.

<그림 2.3(2)-5 새로운 프로젝트 생성>

C:\MyChip Station Pro2005\Layout\tecfile\SCMOS\_SCN4ME\_SUBM.TEC를 선택하고 열 기를 누른다. Default.tec파일에서 사용자가 편집해서 사용해도 된다.

<그림 2.3(2)-6 TEC 파일 불러오기>

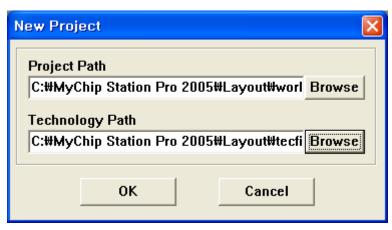

New Project창에 아래 그림과 같이 입력이 완료되면 OK를 누른다.

<그림 2.3(2)-7 TEC 파일 불러오기>

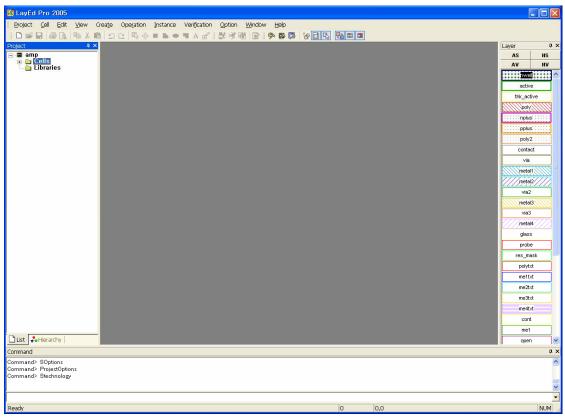

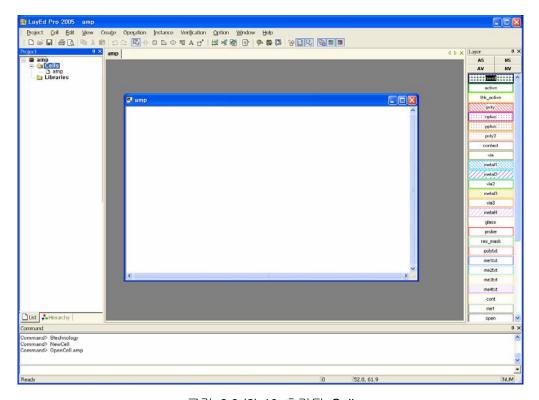

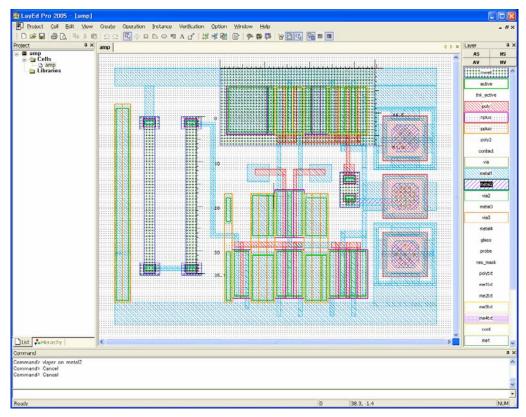

LayEd Pro창의 Project창에 amp Project가 생기고, Layer창에 Layer가 생긴 것을 볼 수 있다.

<그림 2.3(2)-8 생성된 프로젝트와 Layer>

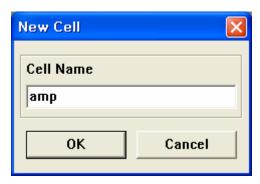

#### iii. New Cell

Menu → Cell → New Cell선택한 후 New Cell창에서 Cell Name에 Inv 쓰고 OK를 누른다.

<그림 2.3.(2)-9 Cell 추가>

<그림 2.3.(2)-10 추가된 Cell>

그림 2.3.(2)-10 화면까지 완성됐으면 Layout 설계준비가 끝났다. 설계를 시작하기 전에 menu → option → Project option에서 Grid (Layout창의 격자 사이의 간격)설정이 얼마로 되어 있는지 확인한다.

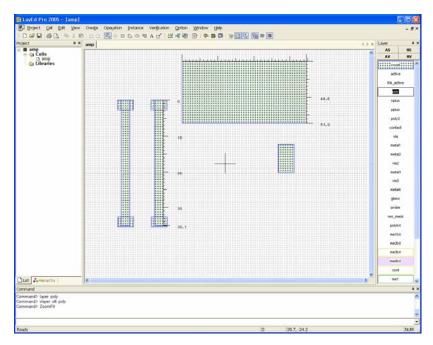

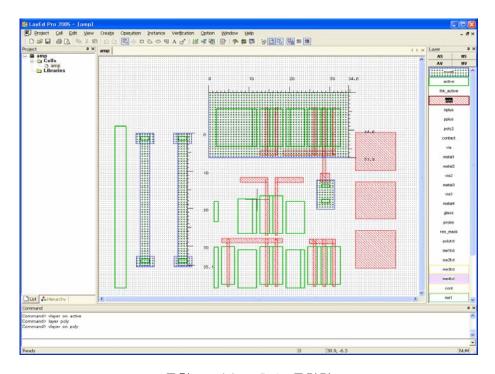

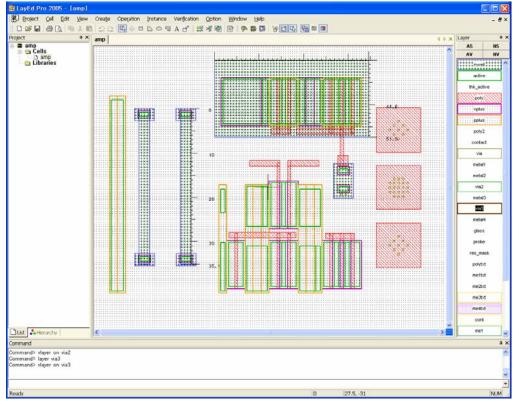

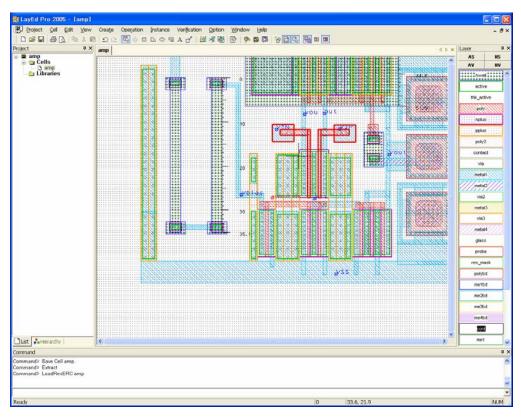

#### ② Layout 설계

Schematic회로를 보고 amp Layout을 설계한다. 모든 그림은 설계 규칙에 맞게 그려야 한다. 주어진 그림의 크기와 간격을 참고 한다. 직접 그려서 설계하는 방법 말고 Command창에 명령어를 사용해서 설계하는 방법도 있다. (명령어를 사용하면 Macro나 VBS를 불어와서 설계할수도 있다.) Menu → View → Ruler → Draw Ruler를 선택하여 길이를 잰다.

## i. Nwell 그리기

Layer Panel의 nwell을 선택한 후 Toolbar의 Rectangle을 선택하여 그림 2.3.(2)-11과 같이 그린다.

<그림 2.3.(2)-11 N-well 그리기>

# ii. Active 그리기

Layer Panel의 active를 선택한 후 Toolbar의 Rectangle을 선택하여 그림2.3.(2)-12 과 같이 그린다.

<그림 2.3.(2)-12 Active 그리기>

# iii. Poly 그리기

Layer Panel의 poly를 선택한 후 Toolbar의 Rectangle을 선택하여 그림 2.3.(2)-13과 같이 그린다.

<그림 2.3.(2)-13 Poly 그리기>

## iv. Npuls, Ppuls 그리기

Layer Panel의 Npuls, Ppuls를 선택한 후 Toolbar의 Rectangle을 선택하여 그림 2.3.(2)-14 과 같이 그린다.

<그림 2.3.(2)-14 Nplus, Pplus 그리기>

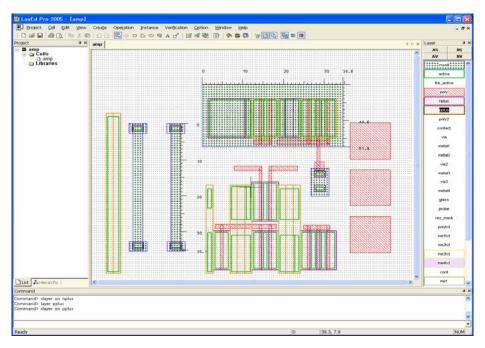

## v. Contact 그리기

Layer Panel의 Contact을 선택한 후 Toolbar의 Rectangle을 선택하여 그림2.3.(2)-15, 그림 2.3.(2)-16과 같이 그린다.

<그림 2.3.(2)-15 Contact 그리기>

<그림 2.3.(2)-16 Via 그리기>

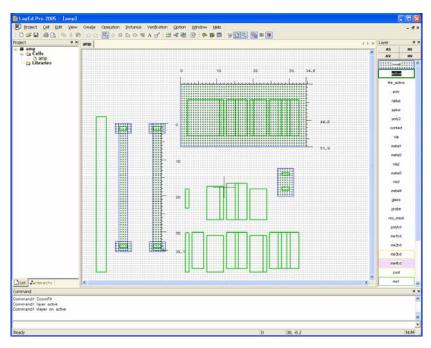

## vi. Metal 그리기

Layer Panel의 Metal1을 선택한 후 Toolbar의 Rectangle을 선택하여 그림 2.3.(2)-17과 같이 그린다. Metal2 역시 같은 방법으로 그린다.

<그림 2.3.(2)-17 Metal 그리기>

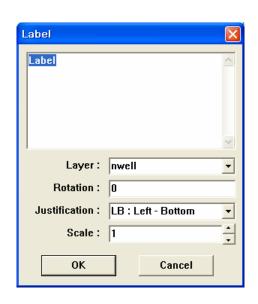

#### vii. Metal text 그리기

Layer Panel의 Me1txt을 선택한 후 Toolbar의 A로 표시된 Label을 선택한 후 Label창에 IN을 쓰고 Justification의 스크롤화살표를 눌러 text의 위치를 정한다.

<그림 2.3.(2)-18 Metal Label 추가>

VIN, VIP, Vbias, vou, out, Vis, Vout, VDD, VSS를 그림 2.3.(2)-19과 같이 만든다.

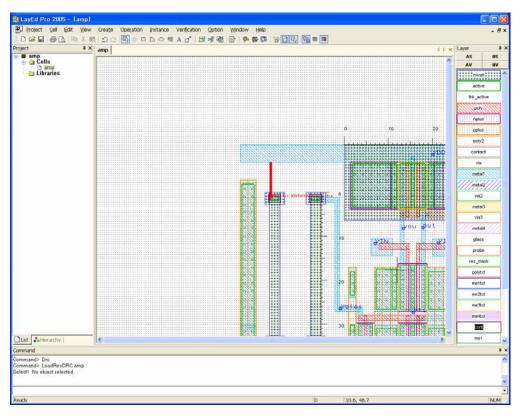

<그림 2.3.(2)-19 완성된 Layout>

완료 후 저장하면 Layout 설계가 완성된다.

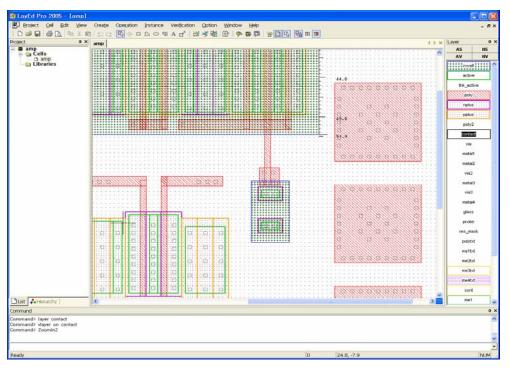

#### ③ Layout 검증

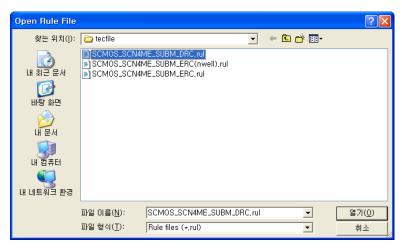

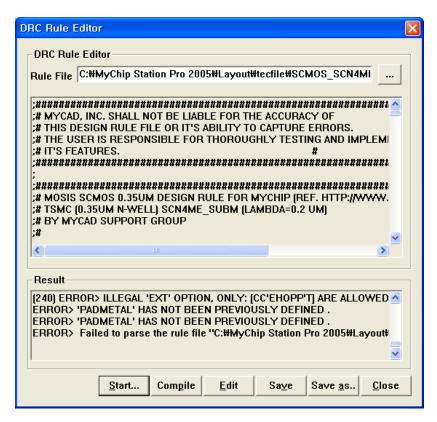

i. DRC (Design Rule Check) - MyDRC Pro

Menu → Verification → DRC를 선택한다. MyDRC Pro창의 Rule 오른쪽의 Browse를 열어

C:\MyChip Station Pro 2005\Layout\tecfile의 SCMOS\_SCN4ME\_SUBM\_DRC.rul을 선택한다.

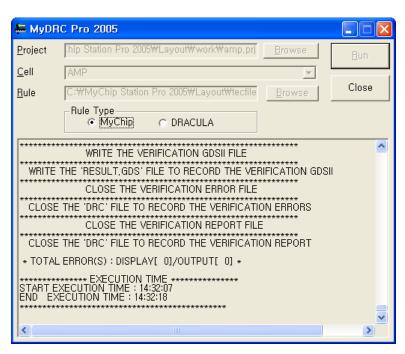

<그림 2.3.(2)-20 DRC check>

MyDRC Pro창의 Rule에 그림 2.3.(2)-21과 같이 DRC.rul파일이 첨가 되면 Run을 누른다.

<그림 2.3.(2)-21 DRC check>

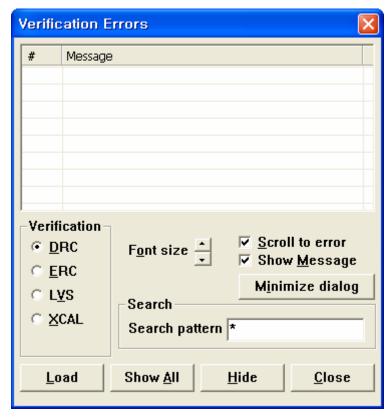

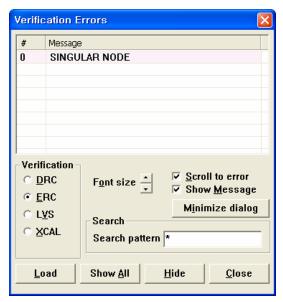

그림 2.3.(2)-21 화면이 나오면 Close를 누른다. 그러면 Verification Errors창이 뜬다.

<그림 2.3.(2)-22 Verification>

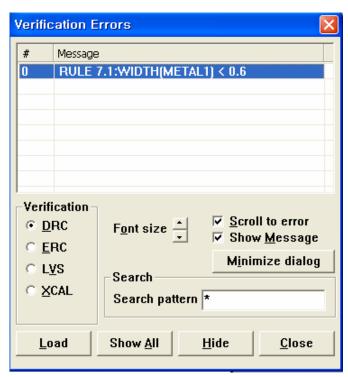

Error가 나오면 Error를 더블 클릭하여 Layout상의 Error발생 지점으로 화면이 이동하면 설계 규칙에 맞게 수정한다.

<그림 2.3.(2)-23 Verification>

<그림 2.3.(2)-24 Verification>

ii. Extract & ERC (Spice Netlist Extract & Electric Rule Check) - LayNet Pro

Menu → Verification → Extract & ERC를 선택한다.

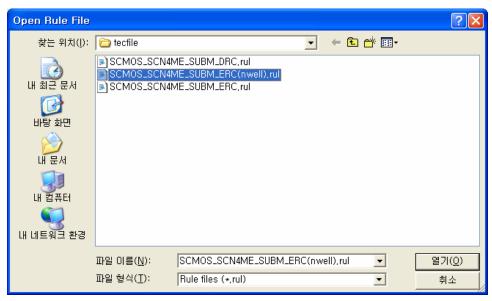

LayNet Pro창의 Rule 오른쪽의 Browse를 누른 후에

C:\MyChip Station Pro 2005\Layout\tecfile\SCMOS\_SCN4ME\_SUBM\_ERC(nwell).rul을 넣는다.

<그림 2.3.(2)-25 ERC check>

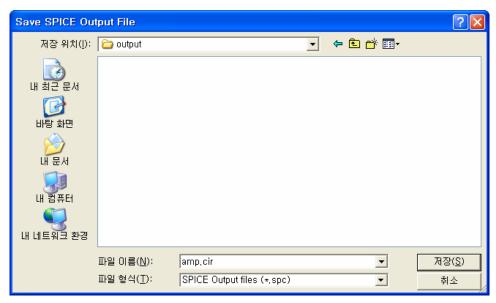

LayNet Pro창의 Output 오른쪽의 Browse를 눌러 C:\MyChip Station Pro 2005\Layout\에 output folder를 만들고 output folder에 파일이름 amp.cir를 쓰고 저장을 누른다.

<그림 2.3.(2)-26 Output 파일 저장>

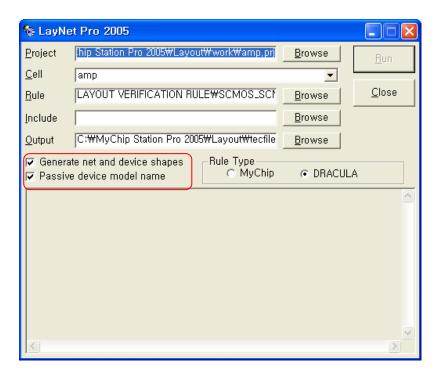

output path의 확장자를 amp.cir로 바꾸고, Generate net and device shapes, Passive device model name을 선택한 후에 Run을 누른다.

<그림 2.3(2)-27 Option 설정>

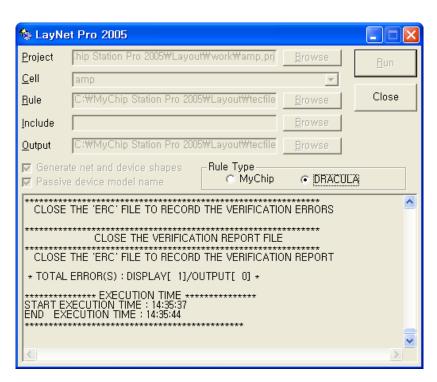

<그림 2.3.(2)-28 실행>

Close를 누르면 Verification Errors창이 뜬다.

<그림 2.3.(2)-29 Verification>

Error가 나오면 Error를 더블 클릭하여 Layout상의 Error발생 지점으로 화면이 이동하면 설계 규칙에 맞게 수정한다.

<그림 2.3.(2)-30 Verification>

## iii. Real Time DRC

Menu → Verification → Real Time DRC → Rule File Load를 선택하여 실행한다. Verification File은 Real Time DRC.rul파일을 사용하던지 SCMOS\_SCN4ME\_SUBM\_DRC.rul을 사용한다. Real Time DRC는 순차적으로 발생하는 Layout의 Error를 바로 수정하면서 DRC를 하는 것을 말한다.

<그림 2.3.(2)-31 Real time DRC>

④ SPICE 시뮬레이션 [MySPICE (Analog Circuit Simulation)] 시작 → 프로그램 → MyAnalogV63 → MySPICE 선택하여 실행시킨다.

<그림 2.3(2)-32 MySpice 실행>

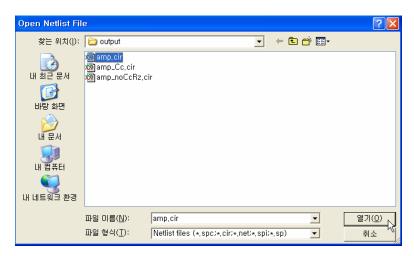

#### i. Open File

Menu → File → Open을 선택한 후 열기 창에서 C:\MyChip Station Pro 2005\Layout\output 의 amp.cir을 선택한 후 열기를 누른다.

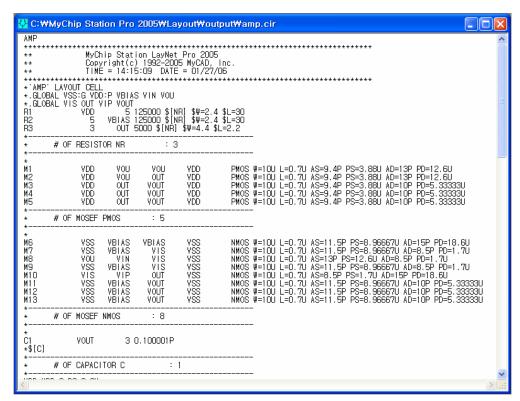

<그림 2.3.(2)-33 Layout에서 추출된 Netlist>

#### ii. SCN4M\_SUMB SPICE BSIM3.txt 포함

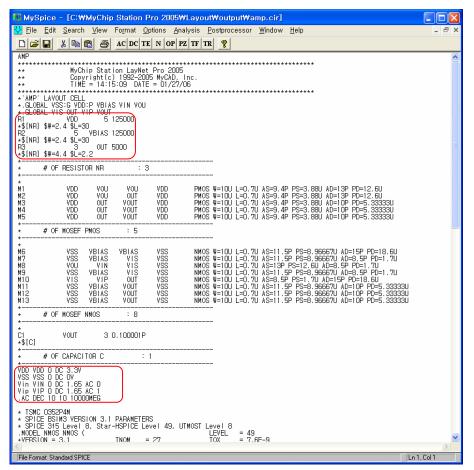

amp.cir파일에 C:\MyChip Station Pro 2005\Layout\spice file의 SCN4M\_SUMB SPICE BSIM3.txt 파일을 붙여 넣고, 시뮬레이션을 하기 위한 signal 및 bias 전압 등을 기입해준다.

또한 시뮬레이션을 하기 위해서 필요 없는 부분들을 아래 그림의 붉은색 사각형 부분과 같이 주석으로 처리를 하고, 입력 변수들을 입력해준다.

<그림 2.3.(2)-34 추출된 Netlist의 내용을 변경>

#### iii. RUN

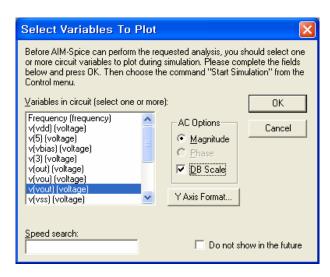

Menu → Analysis → Run Standard Spice File을 선택한다.

Select Variables To Slot창에서 원하는 결과 v[vout][voltage]를 선택하고, AC Options에서 Magnitude를 선택하고, DB Scale을 체크해서 OK를 누른다.

<그림 2.3.(2)-35 출력할 plot 선택>

<그림 2.3.(2)-36>

이전과 같은 방법으로 Select Variables To slot 창에서 원하는 결과 v[vout]를 선택하고, AC Option에서 Phase를 선택해서 OK를 누른다.

<그림 2.3.(2)-37 출력할 plot 선택>

<그림 2.3.(2)-38 >

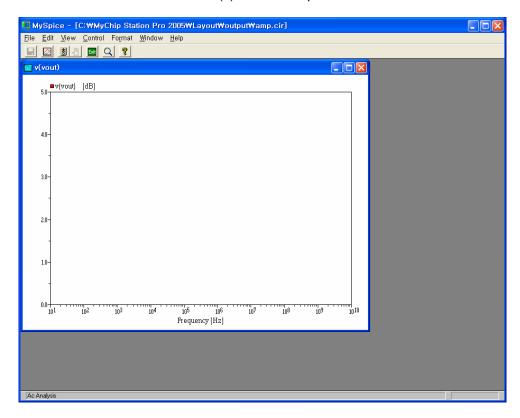

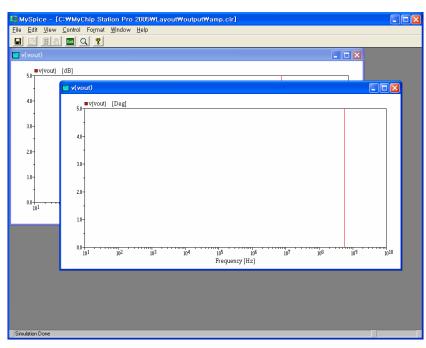

그림 2.3.(2)-38과 같이 시뮬레이션 결과를 출력하기 위한 모든 창들이 나타나면 menu → Control → Start Simulation을 선택한다.

<그림 2.3.(2)-39 실행결과>

#### iv. 결과확인

Simulation Statistics창을 확인하고 OK를 누르면 시뮬레이션이 완료된다.

<그림 2.3.(2)-40 실행결과>

이때 화면상에 결과값이 나타나지 않을 경우에는 menu → Format → Auto Scale을 선택하면 결과값이 아래 그림과 같이 나타난다.

<그림 2.3.(2)-41 출력파형>

#### (3) Layout과 Schematic 비교분석

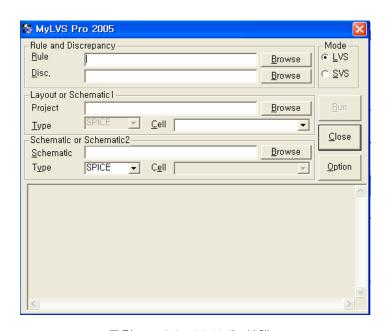

① Netlist 비교 [MyLVS (Hierarchical Layout Versus Schematic Netlist Comparator)]

MyLVS는 Layout과 Schematic에서 추출된 Netlist를 비교한다. LayEd Pro 2005에서 Menu →

Verification → LVS를 선택 하면 MyLVS Pro창이 뜬다.

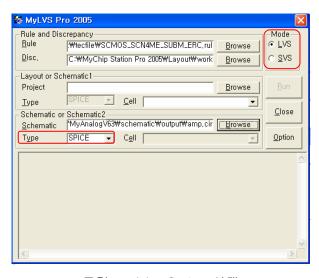

<그림 2.3.(3)-1 MyLVS 실행>

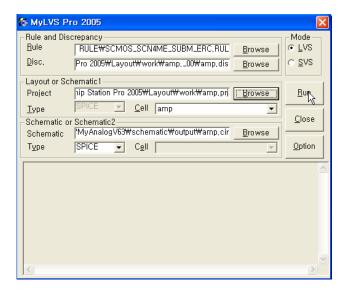

#### i. Rule & Discrepancy

Rule에는 LayNet Pro에서 사용한 rule 파일을 사용한다. C:\MyChip Station Pro 2005\Layout\tecfile\SCMOS\_SCN4ME\_SUBM\_ERC.rul을 선택한다.

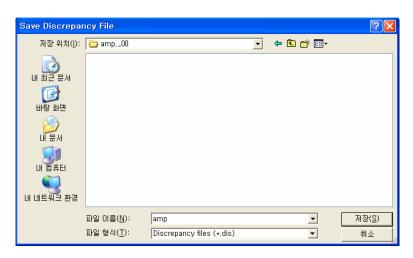

Disc(Discrepancy)파일은 두 Netlist의 비교 결과 정보를 말한다. Rule이 정보를 보관할 수 있도록 파일을 정해준다. C:\MyChip Station Pro 2005\Layout\Work\amp.\_00에 amp.dis로 정한다. amp.\_00 파일은 LayEd에서 amp Cell 생성시 생기는 폴더이다.

<그림 2.3.(3)-2 Discrepancy 파일 생성>

#### ii. Layout or Schematic1

Project에서 C:\MyChip Station Pro 2005\Layout\work\amp.prj를 불러온다.

여기에는 Layout에서 만들었던 Project와 Cell이 자동으로 저장되어 있다. 그러나 SVS를 하려면 Schematic Library를 넣으면 된다. Type란에는 어떤 종류의 Spice를 사용할 것인 지 결정한다. 여기서는 Spice를 사용하므로 선택되어 있다.

#### iii. Schematic or Schematic2

Schematic Editor에서 추출한 Netlist를 불러온다.

C:\MyAnalogV63\schematic\output\amp.cir을 불러온다. (Include.inc file이 포함되지 않은 파일을 불러온다. MOS model과는 비교하는데 관계가 없다.)

<그림 2.3.(3)-3 비교할 Netlist 파일을 불러온다>

Type란에는 Spice를 선택한다. CDL, HSPICE, PSPICE Type의 Schematic Netlist도 비교가능하다.

<그림 2.3(3)-4 Option 선택>

### iv. Mode

LVS (Layout Versus Schematic)와 SVS (Schematic Versus Schematic) 두 가지를 다 비교할 수 있다. 여기서는 LVS를 선택한다.

## v. Option

위 부분에는 회로의 구조변경에 대한 부분이고, 아랫부분은 두 **Netlist**상의 크기 차이 허용범위를 나타내는 부분이다. **OK**를 클릭한다.

<그림 2.3.(3)-5 Option 선택>

<그림 2.3.(3)-6 실행>

그림 2.3.(3)-6과 같이 작성한 후 Run을 눌러 실행시킨다.

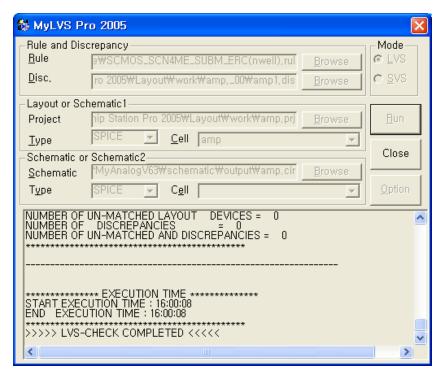

② Discrepancy 파일 확인MyLVS가 완료된 후 Message창에서 Error를 확인할 수 있다.

<그림 2.3.(3)-7 실행결과>

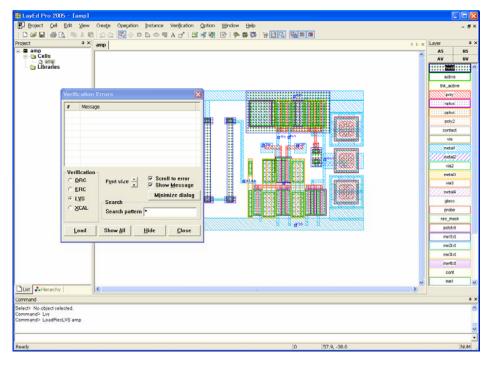

확인 후 Close를 누르면 Verification Errors창이 뜬다. Message창의 Error를 더블 클릭하면 Layout상의 Error지점으로 화면이 이동한다.

<그림 2.3.(3)-8 Verification>

# ③ Layout Spice Simulation과 Schematic Spice Simulation비교

<그림 2.3.(3)-9 결과파형(from layout)>

<그림 2.3.(3)-10 결과파형(from schematic)>

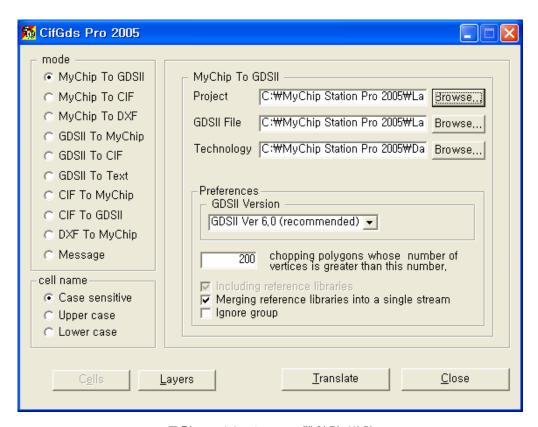

# (4) Layout data 변환

#### 1 CifGDS Pro

MyChip Station Pro → CifGDS Pro ( Data Converter로서 MyChip의 Layout설계를 Mask제작을 위한 파일(GDSII, CIF, DXF)로 변환 할 수 있으며, 이러한 파일을 MyChip으로 변환 할 수도 있다. 또한 파일들 상호변환도 가능하다) 실행 시킨다.

여기서는 MyChip To GDSII로 변환하는 예를 보이기로 한다.

#### i. Mode

MyChip To GDSII을 선택한다.

# ii. MyChip To GDSII

Project는 C:\MyChip Station Pro 2005\Layout\Work\amp.prj를 선택한다. GDSII File은 Work folder에 amp.gds로 Technology는 SCMOS\_SCN4ME\_SUBM.TEC으로 자동 지정된다.

### iii. Preferences

GDSII Version은 Mask제작 방식에 맞는 버전을 선택한다. 여기서는 6.0버전을 선택한다.

### iv. Cell name

Case sensitive를 선택한다.

<그림 2.3.(4)-1 Layout 데이터 변환>

그림 2.3.(4)-1과 같이 완료되면 Translate를 눌러 실행시킨다.

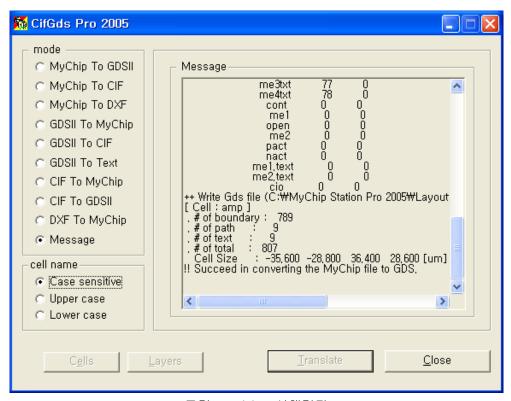

<그림 2.3.(4)-2 실행결과>

Layer mapping결과를 볼 수 있다. 확인이 됐으면 Close를 눌러 창을 닫은 후 C:\MyChip Station Pro 2005\Layout\Work에 amp.gds를 확인한다.

<그림 2.3.(4)-3 실행결과 파일이 생성된다.>

# **APPENDIX**

| Α | Technology File                                         |

|---|---------------------------------------------------------|

| • | A.1. SCMOS_SCN4ME_SUBM.TEC                              |

|   | #                                                       |

|   | % definition                                            |

|   | #                                                       |

|   | nwell                                                   |

|   | active                                                  |

|   | thk_active                                              |

|   | poly                                                    |

|   | nplus                                                   |

|   | pplus                                                   |

|   | poly2                                                   |

|   | contact                                                 |

|   | via                                                     |

|   | metal1                                                  |

|   | metal2                                                  |

|   | via2                                                    |

|   | metal3                                                  |

|   | via3                                                    |

|   | metal4                                                  |

|   | glass                                                   |

|   | probe                                                   |

|   | res_mask                                                |

|   | polytxt                                                 |

|   | me1txt                                                  |

|   | me2txt                                                  |

|   | me3txt                                                  |

|   | me4txt                                                  |

|   | #                                                       |

|   | % stipple_file                                          |

|   | #                                                       |

|   | C:\MyChip Station Pro 2005\Layout\tecfile\stipple.lst # |

|   | % cif_name                                              |

|   | #                                                       |

|   | nwell CWN                                               |

|   | active CAA                                              |

|   |                                                         |

| thk_active                                                                                   |                         | CUK             |

|----------------------------------------------------------------------------------------------|-------------------------|-----------------|

| poly                                                                                         | CPG                     |                 |

| nplus                                                                                        | CSN                     |                 |

| pplus                                                                                        | CSP                     |                 |

| poly2                                                                                        | OPS                     |                 |

| contact                                                                                      |                         | CCC             |

| via                                                                                          | CV1                     |                 |

| metal1                                                                                       |                         | CM1             |

| metal2                                                                                       |                         | CM2             |

| via2                                                                                         | CV2                     |                 |

| metal3                                                                                       |                         | СМЗ             |

| via3                                                                                         | CV3                     |                 |

| metal4                                                                                       |                         | CM4             |

| glass                                                                                        | COG                     |                 |

| probe                                                                                        | XP                      |                 |

| res_mask                                                                                     |                         | CRM             |

| polytxt                                                                                      |                         | CPT             |

| me1txt                                                                                       |                         | CM1T            |

| me2txt                                                                                       |                         | CM2T            |

| me3txt                                                                                       |                         | СМЗТ            |

|                                                                                              |                         |                 |

| me4txt                                                                                       |                         | CM4T            |

| me4txt<br>#                                                                                  |                         | CM4T            |

|                                                                                              | <br>me                  | CM4T            |

| #                                                                                            | ne                      | CM4T            |

| #% dxf_nar                                                                                   | me<br>DXF               | CM4T            |

| #<br>% dxf_nar<br>#                                                                          |                         | CM4T            |

| #<br>% dxf_nar<br>#<br>nwell                                                                 | DXF                     | CM4T            |

| #<br>% dxf_nar<br>#<br>nwell<br>active                                                       | DXF                     |                 |

| #nwell active thk_active                                                                     | DXF<br>DXF              |                 |

| # % dxf_nar # nwell active thk_active poly                                                   | DXF<br>DXF              |                 |

| # % dxf_nar # nwell active thk_active poly nplus                                             | DXF DXF DXF             |                 |

| #nwell active thk_active poly nplus pplus                                                    | DXF DXF DXF DXF DXF     |                 |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2                                 | DXF DXF DXF DXF DXF     | DXF             |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2 contact                         | DXF DXF DXF DXF DXF DXF | DXF             |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2 contact via                     | DXF DXF DXF DXF DXF DXF | DXF             |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2 contact via metal1              | DXF DXF DXF DXF DXF DXF | DXF<br>DXF      |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2 contact via metal1 metal2       | DXF DXF DXF DXF DXF DXF | DXF<br>DXF      |

| # % dxf_nar # nwell active thk_active poly nplus pplus poly2 contact via metal1 metal2 via2  | DXF DXF DXF DXF DXF DXF | DXF DXF DXF DXF |

| # % dxf_nar # nwell active thk_active poly nplus poly2 contact via metal1 metal2 via2 metal3 | DXF DXF DXF DXF DXF DXF | DXF DXF DXF DXF |

| glass      | DXF |       |  |

|------------|-----|-------|--|

| probe      | DXF |       |  |

| res_mask   |     | DXF   |  |

| polytxt    |     | DXF   |  |

| me1txt     |     | DXF   |  |

| me2txt     |     | DXF   |  |

| me3txt     |     | DXF   |  |

| me4txt     |     | DXF   |  |

| #          |     |       |  |

| % gds_nur  | m   |       |  |

| #          |     |       |  |

| nwell      | 42  |       |  |

| active     | 43  |       |  |

| thk_active |     | 60    |  |

| poly       | 46  |       |  |

| nplus      | 45  |       |  |

| pplus      | 44  |       |  |

| poly2      | 56  |       |  |

| contact    |     | 25    |  |

| via        | 50  |       |  |

| metal1     |     | 49    |  |

| metal2     |     | 51    |  |

| via2       | 61  |       |  |

| metal3     |     | 62    |  |

| via3       | 30  |       |  |

| metal4     |     | 31    |  |

| glass      | 34  |       |  |

| probe      | 26  |       |  |

| res_mask   |     | 79    |  |

| polytxt    |     | 74    |  |

| me1txt     |     | 75    |  |

| me2txt     |     | 76    |  |

| me3txt     |     | 77    |  |

| me4txt     |     | 78    |  |

| #          |     |       |  |

| % color    |     |       |  |

| #          |     |       |  |

| nwell      | 255 | 255 0 |  |

| active     | 0   | 198 0 |  |

| thk_active     |          | 255      | 255 | 0   |

|----------------|----------|----------|-----|-----|

| poly           | 255      | 0        | 0   |     |

| nplus          | 196      | 0        | 196 |     |

| pplus          | 255      | 161      | 0   |     |

| poly2          | 255      | 128      | 64  |     |

| contact        |          | 128      | 128 | 128 |

| via            | 125      | 125      | 0   |     |

| metal1         |          | 0        | 0   | 250 |

| metal2         |          | 0        | 255 | 255 |

| via2           | 0        | 198      | 0   |     |

| metal3         |          | 255      | 213 | 0   |

| via3           | 255      | 128      | 0   |     |

| metal4         |          | 212      | 153 | 255 |

| glass          | 255      | 255      | 157 |     |

| probe          | 255      | 0        | 0   |     |

| res_mask       |          | 0        | 255 | 0   |

| polytxt        |          | 255      | 0   | 0   |

| me1txt         |          | 0        | 0   | 255 |

| me2txt         |          | 0        | 204 | 204 |

| me3txt         |          | 255      | 213 | 0   |

| me4txt         |          | 212      | 153 | 255 |

| #              |          |          |     |     |

| % fill_style   | )        |          |     |     |

| #              |          |          |     |     |

| nwell          | empty    |          |     |     |

| active         | stipple_ | 9        |     |     |

| thk_active     |          | empty    |     |     |

| poly           | stipple_ | 9        |     |     |

| nplus          | stipple_ | .3       |     |     |

| pplus          | stipple_ | .3       |     |     |

| poly2          | stipple_ | 10       |     |     |

| contact        |          | solid    |     |     |

| via            | solid    |          |     |     |

| metal1         |          | stipple_ | 2   |     |

| metal2         |          | stipple_ | .3  |     |

| via2           | solid    |          |     |     |

| 10             |          |          |     |     |

| metal3         |          | stipple_ | 2   |     |

| metai3<br>via3 | solid    | stipple_ | 2   |     |

stipple\_3

metal4

| glass      | solid |          |     |     |

|------------|-------|----------|-----|-----|

| probe      | empty |          |     |     |

| res_mask   |       | empty    |     |     |

| polytxt    |       | empty    |     |     |

| me1txt     |       | empty    |     |     |

| me2txt     |       | empty    |     |     |

| me3txt     |       | empty    |     |     |

| me4txt     |       | stipple_ | _5  |     |

| #          |       |          |     |     |

| % line_col | or    |          |     |     |

| #          |       |          |     |     |

| nwell      | 255   | 255      | 0   |     |

| active     | 0     | 198      | 0   |     |

| thk_active |       | 255      | 255 | 0   |

| poly       | 255   | 0        | 0   |     |

| nplus      | 196   | 0        | 196 |     |

| pplus      | 255   | 161      | 0   |     |

| poly2      | 255   | 128      | 64  |     |

| contact    |       | 128      | 128 | 128 |

| via        | 125   | 125      | 0   |     |

| metal1     |       | 0        | 0   | 250 |

| metal2     |       | 0        | 255 | 255 |

| via2       | 0     | 198      | 0   |     |

| metal3     |       | 255      | 213 | 0   |

| via3       | 255   | 128      | 0   |     |

| metal4     |       | 212      | 153 | 255 |

| glass      | 255   | 255      | 157 |     |

| probe      | 255   | 0        | 0   |     |

| res_mask   |       | 0        | 255 | 0   |

| polytxt    |       | 255      | 0   | 0   |

| me1txt     |       | 0        | 0   | 255 |

| me2txt     |       | 0        | 204 | 204 |

| me3txt     |       | 255      | 213 | 0   |

| me4txt     |       | 212      | 153 | 255 |

| #          |       |          |     |     |

| % line_sty |       |          |     |     |

| #          |       |          |     |     |

| nwell      | 0     |          |     |     |

| active     | 0     |          |     |     |

| thk_active                                                                                                |                            | 0           |  |

|-----------------------------------------------------------------------------------------------------------|----------------------------|-------------|--|

| poly                                                                                                      | 0                          | -           |  |

| nplus                                                                                                     | 0                          |             |  |

| pplus                                                                                                     | 0                          |             |  |

| poly2                                                                                                     | 0                          |             |  |

| contact                                                                                                   |                            | 0           |  |

| via                                                                                                       | 0                          |             |  |

| metal1                                                                                                    |                            | 0           |  |

| metal2                                                                                                    |                            | 0           |  |

| via2                                                                                                      | 0                          |             |  |

| metal3                                                                                                    |                            | 0           |  |

| via3                                                                                                      | 0                          |             |  |

| metal4                                                                                                    |                            | 0           |  |

| glass                                                                                                     | 0                          |             |  |

| probe                                                                                                     | 0                          |             |  |

| res_mask                                                                                                  |                            | 0           |  |

| polytxt                                                                                                   |                            | 0           |  |

| me1txt                                                                                                    |                            | 0           |  |

| me2txt                                                                                                    |                            | 0           |  |

| me3txt                                                                                                    |                            | 0           |  |

| IIIGOIXI                                                                                                  |                            | U           |  |

| me4txt                                                                                                    |                            | 0           |  |

|                                                                                                           |                            |             |  |

| me4txt                                                                                                    | dth                        |             |  |

| me4txt<br>#                                                                                               | dth                        |             |  |

| me4txt<br>#<br>% line_wi                                                                                  | dth<br>1                   |             |  |

| me4txt<br>#<br>% line_wi<br>#                                                                             |                            |             |  |

| me4txt<br>#<br>% line_wi<br>#                                                                             | 1                          |             |  |

| me4txt # % line_wi # nwell active                                                                         | 1                          | 0           |  |

| me4txt # % line_wi # nwell active thk_active                                                              | 1<br>1                     | 0           |  |

| me4txt # % line_wi # nwell active thk_active poly                                                         | 1<br>1<br>1                | 0           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus                                                   | 1<br>1<br>1                | 0           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus                                             | 1<br>1<br>1<br>1<br>1      | 0           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2                                       | 1<br>1<br>1<br>1<br>1      | 1           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2 contact                               | 1<br>1<br>1<br>1<br>1<br>1 | 1           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2 contact via                           | 1<br>1<br>1<br>1<br>1<br>1 | 1           |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2 contact via metal1                    | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1      |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1 metal2       | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1      |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2 contact via metal1 metal2 via2        | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1 |  |

| me4txt # % line_wi # nwell active thk_active poly nplus pplus poly2 contact via metal1 metal2 via2 metal3 | 1<br>1<br>1<br>1<br>1<br>1 | 1<br>1<br>1 |  |

| glass      | 1        |     |   |   |

|------------|----------|-----|---|---|

| probe      | 1        |     |   |   |

| res_mask   |          | 1   |   |   |

| polytxt    |          | 1   |   |   |

| me1txt     |          | 1   |   |   |

| me2txt     |          | 1   |   |   |

| me3txt     |          | 1   |   |   |

| me4txt     |          | 1   |   |   |

| #          |          |     |   |   |

| % line_co  | olor_sel |     |   |   |

| #          |          |     |   |   |

| nwell      | 255      | 0   | 0 |   |

| active     | 255      | 0   | 0 |   |

| thk_active |          | 255 | 0 | 0 |

| poly       | 255      | 0   | 0 |   |

| nplus      | 255      | 0   | 0 |   |

| pplus      | 255      | 0   | 0 |   |

| poly2      | 255      | 0   | 0 |   |

| contact    |          | 255 | 0 | 0 |

| via        | 255      | 0   | 0 |   |

| metal1     |          | 255 | 0 | 0 |

| metal2     |          | 255 | 0 | 0 |

| via2       | 255      | 0   | 0 |   |

| metal3     |          | 255 | 0 | 0 |

| via3       | 255      | 0   | 0 |   |

| metal4     |          | 255 | 0 | 0 |

| glass      | 255      | 0   | 0 |   |

| probe      | 255      | 0   | 0 |   |

| res_mask   |          | 255 | 0 | 0 |

| polytxt    |          | 255 | 0 | 0 |

| me1txt     |          | 255 | 0 | 0 |

| me2txt     |          | 255 | 0 | 0 |

| me3txt     |          | 255 | 0 | 0 |

| me4txt     |          | 255 | 0 | 0 |

| #          |          |     |   |   |

| % line_st  | yle_sel  |     |   |   |

| #          |          |     |   |   |

| nwell      | 0        |     |   |   |

| active     | 0        |     |   |   |

|            |          |     |   |   |

| thk_active                                                                                                 |                                 | 0                |

|------------------------------------------------------------------------------------------------------------|---------------------------------|------------------|

| poly                                                                                                       | 0                               |                  |

| nplus                                                                                                      | 0                               |                  |

| pplus                                                                                                      | 0                               |                  |

| poly2                                                                                                      | 0                               |                  |

| contact                                                                                                    |                                 | 0                |

| via                                                                                                        | 0                               |                  |

| metal1                                                                                                     |                                 | 0                |

| metal2                                                                                                     |                                 | 0                |

| via2                                                                                                       | 0                               |                  |

| metal3                                                                                                     |                                 | 0                |

| via3                                                                                                       | 0                               |                  |

| metal4                                                                                                     |                                 | 0                |

| glass                                                                                                      | 0                               |                  |

| probe                                                                                                      | 0                               |                  |

| res_mask                                                                                                   |                                 | 0                |

| polytxt                                                                                                    |                                 | 0                |

| me1txt                                                                                                     |                                 | 0                |

| me2txt                                                                                                     |                                 | 0                |

| me3txt                                                                                                     |                                 | 0                |

| 1110001                                                                                                    |                                 | J                |

| me4txt                                                                                                     |                                 | 0                |

|                                                                                                            |                                 | 0                |

| me4txt                                                                                                     |                                 | 0                |

| me4txt<br>#%                                                                                               |                                 | 0                |

| me4txt<br>#<br>% line_wid                                                                                  | dth_sel                         | 0                |

| me4txt<br>#<br>% line_wid<br>#                                                                             | dth_sel                         | 0                |

| me4txt<br>#<br>% line_wid<br>#                                                                             | dth_sel<br>3                    | 0                |

| #nwell active                                                                                              | dth_sel<br>3                    | 0                |

| me4txt # % line_wid # nwell active thk_active                                                              | 3<br>3                          | 0                |

| me4txt # % line_wid # nwell active thk_active poly                                                         | 3<br>3<br>3                     | 0                |

| me4txt # % line_wid # nwell active thk_active poly nplus                                                   | 3<br>3<br>3<br>3                | 0                |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus                                             | 3<br>3<br>3<br>3<br>3           | 0                |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus poly2                                       | 3<br>3<br>3<br>3<br>3           | 1                |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus pplus poly2 contact                         | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1                |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus poly2 contact via                           | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1                |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus poly2 contact via metal1                    | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1<br>3<br>3      |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1 metal2       | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1<br>3<br>3      |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1 metal2 via2  | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1<br>3<br>3<br>3 |

| me4txt # % line_wid # nwell active thk_active poly nplus pplus poly2 contact via metal1 metal2 via2 metal3 | 3<br>3<br>3<br>3<br>3<br>3<br>3 | 1<br>3<br>3<br>3 |

| glass      | 1     |       |       |       |     |

|------------|-------|-------|-------|-------|-----|

| probe      | 1     |       |       |       |     |

| res_mask   | •     | 3     |       |       |     |

| polytxt    |       | 3     |       |       |     |

| me1txt     |       | 3     |       |       |     |

| me2txt     |       | 3     |       |       |     |

| me3txt     |       | 3     |       |       |     |

| me4txt     |       | 3     |       |       |     |

| #          |       |       |       |       |     |

| " % path   |       |       |       |       |     |

| #          |       |       |       |       |     |

| "<br>nwell |       | 0     |       | 0.0   |     |

| active     | 1.000 |       |       |       |     |

| thk_active | 1.000 | 1.000 |       |       | 0.0 |

| poly       | 1.000 | 0     |       |       | 0.0 |

| nplus      | 1.000 |       |       |       |     |

| pplus      | 1.000 | 0     | 0.000 | 0.0   |     |

| poly2      | 1.000 |       | 0.000 |       |     |

| contact    | 1.000 | 1.000 | 0     |       | 0.0 |

| via        | 1.000 | 0     | 0.000 |       | 0.0 |

| metal1     |       | 1.000 |       |       | 0.0 |

| metal2     |       | 1.000 |       |       | 0.0 |

| via2       | 1.000 | 0     |       |       |     |

| metal3     |       | 1.000 |       |       | 0.0 |

| via3       | 1.000 | 0     | 0.000 | 0.0   |     |

| metal4     |       | 1.000 | 0     | 0.000 | 0.0 |

| glass      | 1.000 | 0     | 0.000 | 0.0   |     |

| probe      | 1.000 | 0     | 0.000 | 0.0   |     |

| res_mask   |       | 1.000 | 0     | 0.000 | 0.0 |

| polytxt    |       | 1.000 | 0     | 0.000 | 0.0 |

| me1txt     |       | 1.000 | 0     | 0.000 | 0.0 |

| me2txt     |       | 1.000 | 0     | 0.000 | 0.0 |

| me3txt     |       | 1.000 | 0     | 0.000 | 0.0 |

| me4txt     |       | 1.000 | 0     | 0.000 | 0.0 |

| #          |       |       |       |       |     |

| % datatyp  | е     |       |       |       |     |

| #          |       |       |       |       |     |

| nwell      | 0     |       |       |       |     |

| active     | 0     |       |       |       |     |

| thk_active                                                                                                |                                               | 0                             |

|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------|

| poly                                                                                                      | 0                                             |                               |

| nplus                                                                                                     | 0                                             |                               |

| pplus                                                                                                     | 0                                             |                               |

| poly2                                                                                                     | 0                                             |                               |

| contact                                                                                                   |                                               | 0                             |

| via                                                                                                       | 0                                             |                               |

| metal1                                                                                                    |                                               | 0                             |

| metal2                                                                                                    |                                               | 0                             |

| via2                                                                                                      | 0                                             |                               |

| metal3                                                                                                    |                                               | 0                             |

| via3                                                                                                      | 0                                             |                               |

| metal4                                                                                                    |                                               | 0                             |

| glass                                                                                                     | 0                                             |                               |

| probe                                                                                                     | 0                                             |                               |

| res_mask                                                                                                  |                                               | 0                             |

| polytxt                                                                                                   |                                               | 0                             |

| me1txt                                                                                                    |                                               | 0                             |

| me2txt                                                                                                    |                                               | 0                             |

| me3txt                                                                                                    |                                               | 0                             |

| mesixi                                                                                                    |                                               | U                             |

| me4txt                                                                                                    |                                               | 0                             |

|                                                                                                           |                                               |                               |

| me4txt                                                                                                    |                                               |                               |

| me4txt<br>#                                                                                               |                                               |                               |

| me4txt<br>#<br>% textsize                                                                                 |                                               |                               |

| me4txt<br>#<br>% textsize<br>#                                                                            |                                               |                               |

| me4txt<br>#<br>% textsize<br>#nwell                                                                       | 0.5                                           |                               |

| me4txt # % textsize # nwell active                                                                        | 0.5                                           | 0                             |

| me4txt # % textsize # nwell active thk_active                                                             | 0.5<br>0.5                                    | 0                             |

| me4txt # % textsize # nwell active thk_active poly                                                        | 0.5<br>0.5<br>0.5                             | 0                             |

| me4txt # % textsize # nwell active thk_active poly nplus                                                  | 0.5<br>0.5<br>0.5<br>0.5                      | 0                             |

| me4txt # % textsize # nwell active thk_active poly nplus pplus                                            | 0.5<br>0.5<br>0.5<br>0.5<br>0.5               | 0                             |

| me4txt # % textsize # nwell active thk_active poly nplus pplus poly2                                      | 0.5<br>0.5<br>0.5<br>0.5<br>0.5               | 1.0                           |

| me4txt # % textsize # nwell active thk_active poly nplus pplus pplus poly2 contact                        | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5        | 1.0                           |

| me4txt # % textsize # nwell active thk_active poly nplus pplus poly2 contact via                          | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5        | 1.0                           |

| me4txt # % textsize # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1             | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5        | 1.0<br>0.5<br>0.5             |

| me4txt # % textsize # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1 metal2      | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5 | 1.0<br>0.5<br>0.5             |

| me4txt # % textsize # nwell active thk_active poly nplus pplus pplus poly2 contact via metal1 metal2 via2 | 0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5<br>0.5 | 0<br>1.0<br>0.5<br>0.5<br>0.5 |

| glass      | 1.0 |     |     |

|------------|-----|-----|-----|

| probe      | 1.0 |     |     |

| res_mask   |     | 0.5 |     |

| polytxt    |     | 1.0 |     |

| me1txt     |     | 0.5 |     |

| me2txt     |     | 0.5 |     |

| me3txt     |     | 1.0 |     |

| me4txt     |     | 1.0 |     |

| #          |     |     |     |

| % priority |     |     |     |

| #          |     |     |     |

| nwell      | 17  |     |     |

| active     | 11  |     |     |

| thk_active |     | 10  |     |

| poly       | 6   |     |     |

| nplus      | 8   |     |     |

| pplus      | 9   |     |     |

| poly2      | 5   |     |     |

| contact    |     | 15  |     |

| via        | 14  |     |     |

| metal1     |     | 4   |     |

| metal2     |     | 3   |     |

| via2       | 13  |     |     |

| metal3     |     | 2   |     |

| via3       | 12  |     |     |

| metal4     |     | 1   |     |

| glass      | 16  |     |     |

| probe      | 18  |     |     |

| res_mask   |     | 7   |     |

| polytxt    |     | 23  |     |

| me1txt     |     | 22  |     |

| me2txt     |     | 21  |     |

| me3txt     |     | 20  |     |

| me4txt     |     | 19  |     |

| #          |     |     |     |

| % sys_col  | or  |     |     |

| #          |     |     |     |

| background | 0   | 0   | 0   |

| foreground | 255 | 255 | 255 |

|            |     |     |     |

| noselect       | 0        | 128      | 0        |          |          |                                              |

|----------------|----------|----------|----------|----------|----------|----------------------------------------------|

| cellbound      | 255      | 255      | 255      |          |          |                                              |

| grid           | 255      | 255      | 255      |          |          |                                              |

| drag           | 255      | 0        | 0        |          |          |                                              |

| error          | 255      | 0        | 0        |          |          |                                              |

| ruler          | 255      | 255      | 255      |          |          |                                              |

| instance_selec | ct       |          | 255      | 0        | 0        |                                              |

| edge_vertex    |          | 0        | 0        | 255      |          |                                              |

| #              |          |          |          |          |          |                                              |

| % rule         |          |          |          |          |          |                                              |

| #              |          |          |          |          |          |                                              |

| DRC_RULE       |          |          |          |          |          |                                              |

| EXTRACTION     | _RULE    |          |          |          |          |                                              |

| #              |          |          |          |          |          |                                              |

|                |          |          |          |          |          |                                              |

| A.2. STIPPLE.  | LST      |          |          |          |          |                                              |

| stipple_1      | ffff4242 | ffffc3c3 | ffff3c3c | ffff2424 | ffff2424 | ffff3c3c ffffc3c3 ffff4242 ffff4242 ffffc3c3 |

| ffff3c3c       | ffff2424 | ffff2424 | ffff3c3c | ffffc3c3 | ffff4242 | ZigZags [ ZigZags 45 6 6 5 ]                 |